Understanding simulation log file generation, Running a gate-level simulation, Simulating the single dword design – Altera Stratix V Avalon-MM Interface for PCIe Solutions User Manual

Page 18

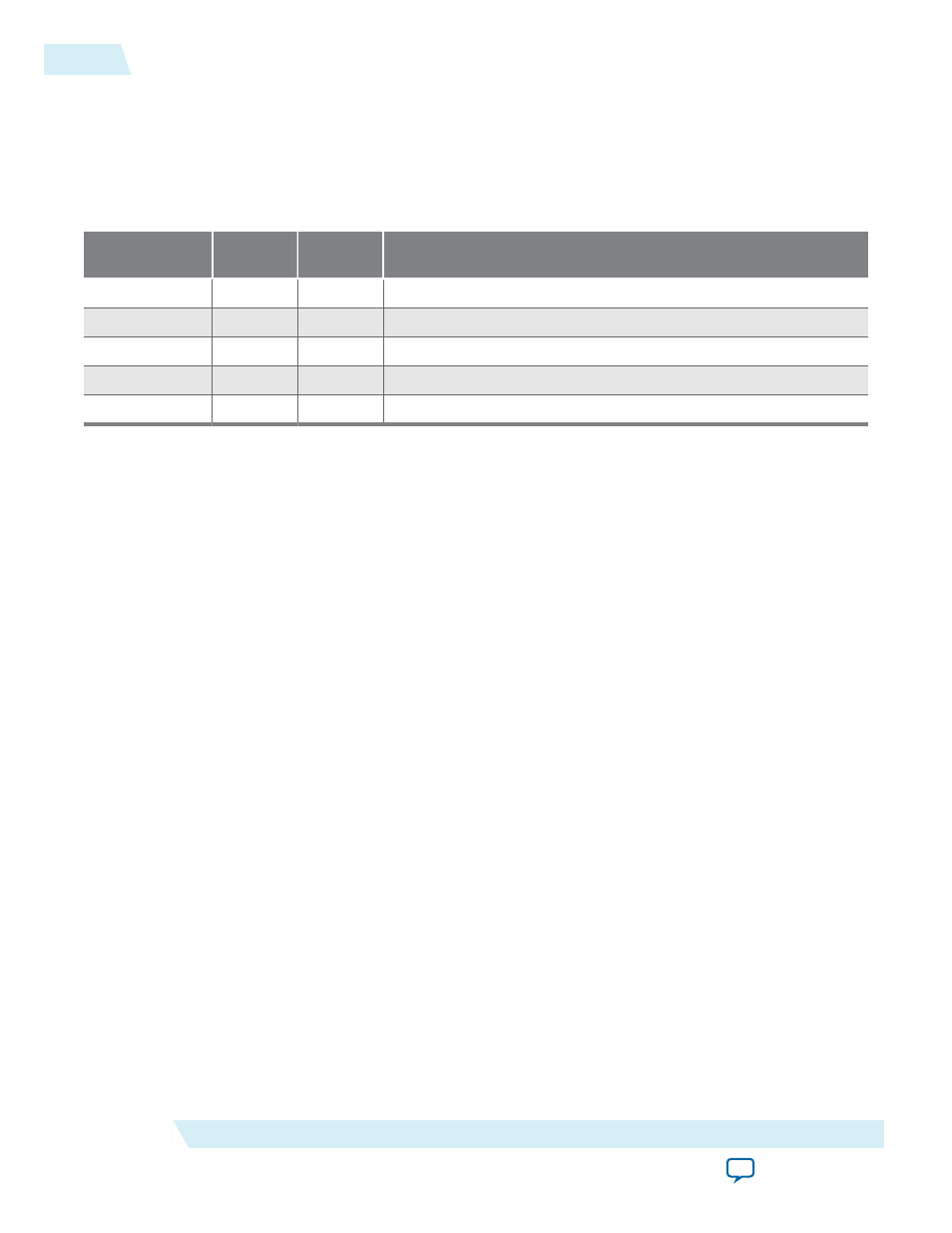

Understanding Simulation Log File Generation

Starting with the Quartus II 14.0 software release, simulation automatically creates a log file,

altpcie_

monitor_

in your simulation directory.

Table 2-2: Sample Simulation Log File Entries

Time

TLP Type

Payload

(Bytes)

TLP Header

17989 RX

CfgRd0

0004

04000001_0000000F_01080008

17989 RX

MRd

0000

00000000_00000000_01080000

18021 RX

CfgRd0

0004

04000001_0000010F_0108002C

18053 RX

CfgRd0

0004

04000001_0000030F_0108003C

18085 RX

MRd

0000

00000000_00000000_0108000C

Running A Gate-Level Simulation

The PCI Express testbenches run simulations at the register transfer level (RTL). However, it is possible to

create you own gate-level simulations. Contact your Altera Sales Representative for instructions and an

example that illustrate how to create a gate-level simulation from the RTL testbench.

Simulating the Single DWord Design

You can use the same testbench to simulate the Completer-Only Single Dword IP core by changing the

settings in the driver file.

1. In a terminal window, change to the

directory.

2. Open altpcietb_bfm_driver_avmm.v in your text editor.

3. To enable target memory tests and specify the completer-only single dword variant, specify the

following parameters:

a.

parameter RUN_TGT_MEM_TST = 1;

b.

parameter RUN_DMA_MEM_TST = 0;

c.

parameter AVALON_MM_LITE = 1;

4. Change to the

directory.

5. Start the ModelSim simulator.

6. To run the simulation, type the following commands in a terminal window:

a.

do msim_setup.tcl

b.

ld_debug

(The debug suffix stops optimizations, improving visibility in the ModelSim waveforms.)

c.

run 140000 ns

2-6

Understanding Simulation Log File Generation

UG-01097_avmm

2014.12.15

Altera Corporation

Getting Started with the Avalon‑MM Stratix V Hard IP for PCI Express