Altera Stratix V Avalon-MM Interface for PCIe Solutions User Manual

Page 46

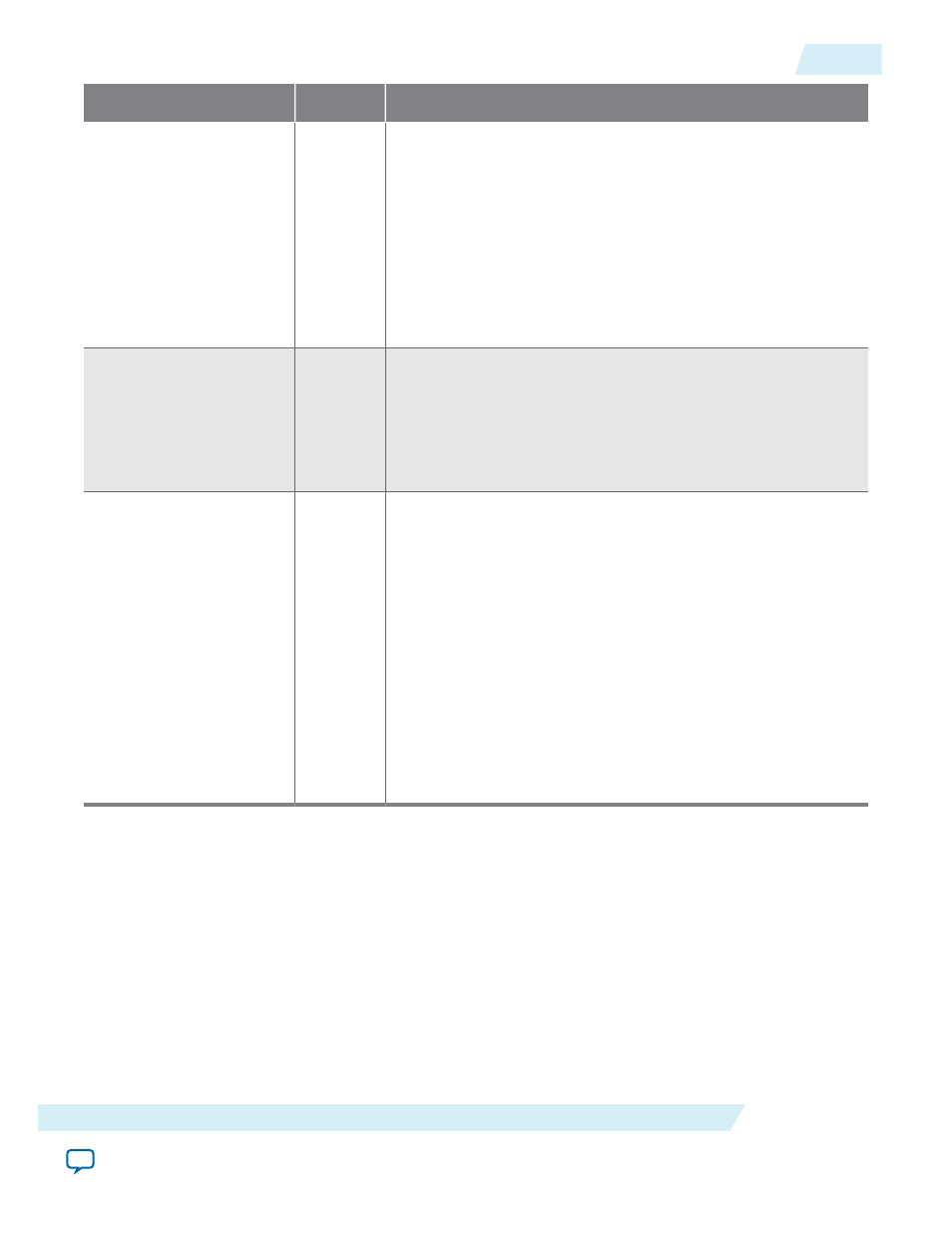

Signal

Direction

Description

• 10011: Loopback.Exit

• 10100: Hot.Reset

• 10101: L0s

• 11001: L2.transmit.Wake

• 11010: Speed.Recovery

• 11011: Recovery.Equalization, Phase 0

• 11100: Recovery.Equalization, Phase 1

• 11101: Recovery.Equalization, Phase 2

• 11110: recovery.Equalization, Phase 3

rx_par_err

Output

When asserted for a single cycle, indicates that a parity error was

detected in a TLP at the input of the RX buffer. This error is

logged as an uncorrectable internal error in the VSEC registers.

For more information, refer to Uncorrectable Internal Error

Status Register. You must reset the Hard IP if this error occurs

because parity errors can leave the Hard IP in an unknown state.

tx_par_err[1:0]

Output

When asserted for a single cycle, indicates a parity error during

TX TLP transmission. These errors are logged in the VSEC

register. The following encodings are defined:

• 2’b10: A parity error was detected by the TX Transaction

Layer. The TLP is nullified and logged as an uncorrectable

internal error in the VSEC registers. For more information,

refer to Uncorrectable Internal Error Status Register.

• 2’b01: Some time later, the parity error is detected by the TX

Data Link Layer which drives 2’b01 to indicate the error.

Reset the IP core when this error is detected. Contact Altera

technical support if resetting becomes unworkable.

Note that not all simulation models assert the Transaction Layer

error bit in conjunction with the Data Link Layer error bit.

Related Information

•

•

UG-01097_avmm

2014.12.15

Reset

4-13

64- or 128-Bit Avalon-MM Interface to the Application Layer

Altera Corporation