Altera Stratix V Avalon-MM Interface for PCIe Solutions User Manual

Page 178

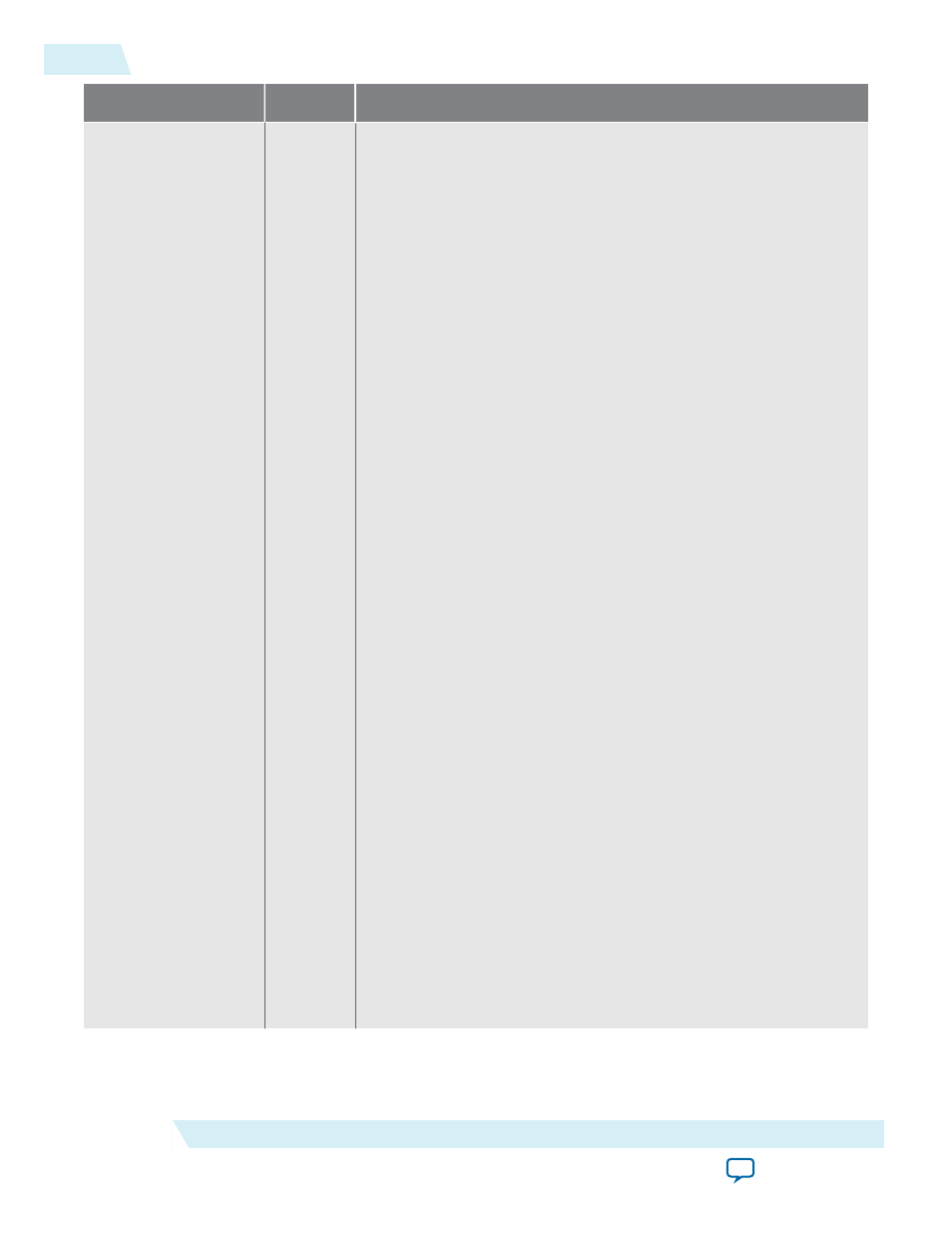

Date

Version

Changes Made

2014.06.30

14.0

Added the following features to the Stratix V Avalon-MM Hard IP

for PCI Express:

• Added access to selected Configuration Space registers and link

status registers through the optional Control Register Access

(CRA) Avalon-MM slave port.

• Added simulation log file,

altpcie_monitor_sv_dlhip_tlp_file_log.log

,

that is automatically generated in your simulation directory. To

simulation in the Quartus II 14.0 software release, you must

regenerate your IP core to create the supporting monitor file the

generates

altpcie_monitor_sv_dlhip_tlp_file_log.log

. Refer to

Understanding Simulation Dump File Generation for details.

• Added parameter to create a reset pulse at power-up when the soft

reset controller is enabled.

• Added optional hard IP status bus that includes signals necessary

to connect the Transceiver Reconfiguration Controller IP Core.

• Added optional hard IP status extension bus which includes

signals that are useful for debugging, including: link training,

status, error, and Configuration Space signals.

• Added support for 64-bit addressing, making address translation

unnecessary.

• Added parameters to enable 256 completion tags with completion

tag checking performed in Application Layer.

• Simulation support for Phase 2 and Phase 3 equalization when

requested by third-party BFM.

• Increased CRA address to 14 bits from 12 bits.

• For

txs_byteenable[

, added restrictions on the legal

patterns of enabled and disabled bytes.

• Clarified the behavior of the

txs_waitrequest

signal.

Made the following changes to the user guide:

• Removed all references to the Avalon-MM interrupt vector

register. This register is not used.

• Corrected addresses for Vendor ID, Device ID, Revision ID, Class

Code, Subsystem Vendor ID and Subsystem Device ID in

Reconfigurable Read-Only Registers.

• Corrected values for Maximum payload size parameter. The sizes

available are 128 or 256 bytes.

• Corrected frequency range for

hip_reconfig_clk

. It should be

100-125 MHz.

• Removed section on Hard IP Reconfiguration. This feature is only

available when you select the Avalon-ST interface.

C-2

Revision History for the Avalon-MM Interface

UG-01097_avmm

2014.12.15

Altera Corporation

Additional Information