Msi and msi-x capabilities – Altera Stratix V Avalon-MM Interface for PCIe Solutions User Manual

Page 28

MSI and MSI-X Capabilities

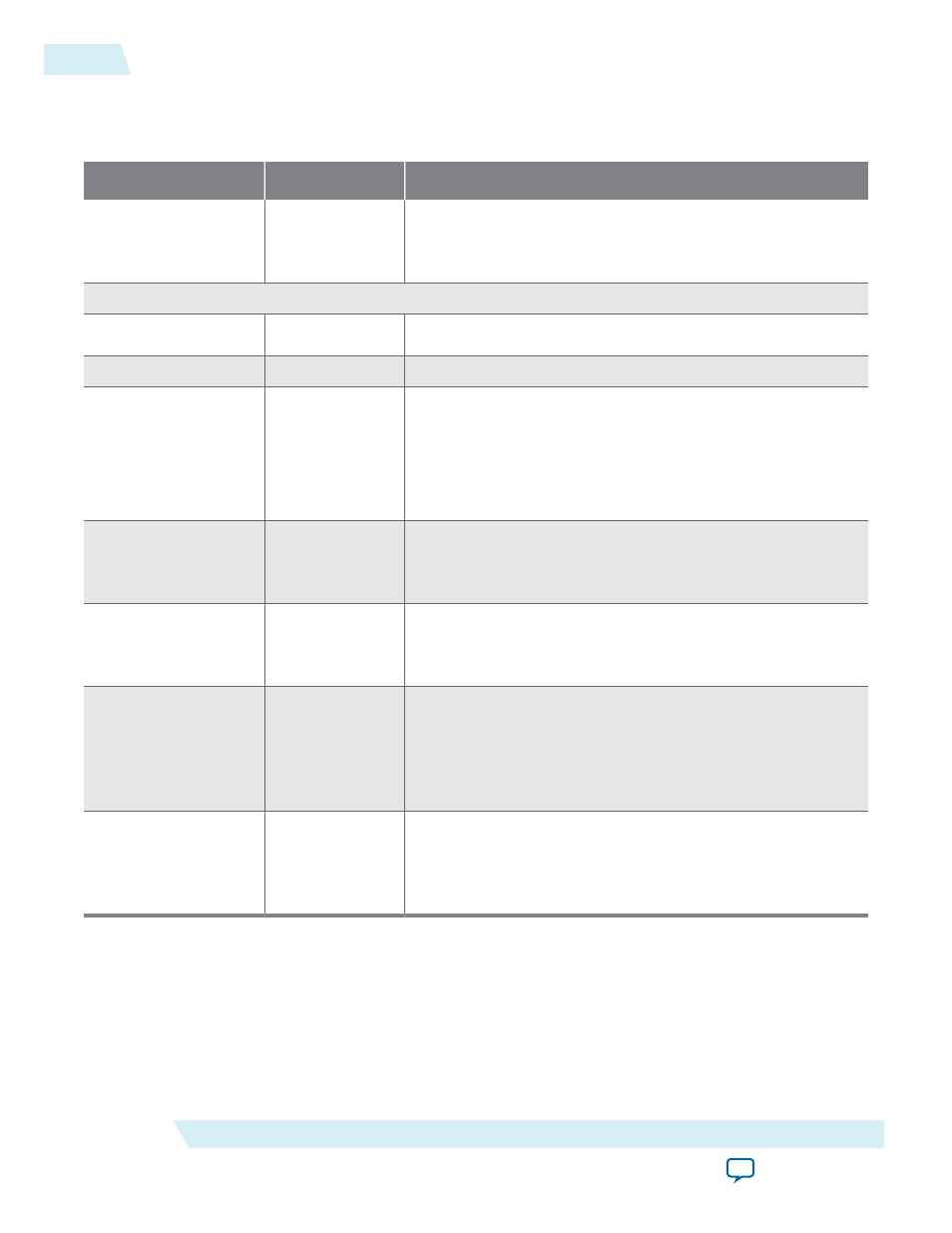

Table 3-7: MSI and MSI-X Capabilities

Parameter

Value

Description

MSI messages

requested

1, 2, 4, 8, 16

Specifies the number of messages the Application Layer can

request. Sets the value of the

Multiple Message Capable

field of the

Message Control

register, 0x050[31:16].

MSI-X Capabilities

Implement MSI-X

On/Off

When On, enables the MSI-X functionality.

Bit Range

Table size

[10:0]

System software reads this field to determine the MSI-X Table

size

value of 2047 indicates a table size of 2048. This field is read-

only. Legal range is 0–2047 (2

11

).

Address offset: 0x068[26:16]

Table Offset

[31:0]

Points to the base of the MSI-X Table. The lower 3 bits of the

table BAR indicator (BIR) are set to zero by software to form a

32-bit qword-aligned offset. This field is read-only.

Table BAR

Indicator

[2:0]

Specifies which one of a function’s BARs, located beginning at

0x10 in Configuration Space, is used to map the MSI-X table

into memory space. This field is read-only. Legal range is 0–5.

Pending Bit Array

(PBA) Offset

[31:0]

Used as an offset from the address contained in one of the

function’s Base Address registers to point to the base of the

MSI-X PBA. The lower 3 bits of the PBA BIR are set to zero by

software to form a 32-bit qword-aligned offset. This field is

read-only.

PBA BAR Indicator

[2:0]

Specifies the function Base Address registers, located

beginning at 0x10 in Configuration Space, that maps the MSI-

X PBA into memory space. This field is read-only. Legal range

is 0–5.

Related Information

3-8

MSI and MSI-X Capabilities

UG-01097_avmm

2014.12.15

Altera Corporation

Parameter Settings