Recommended speed grades – Altera Stratix V Avalon-MM Interface for PCIe Solutions User Manual

Page 11

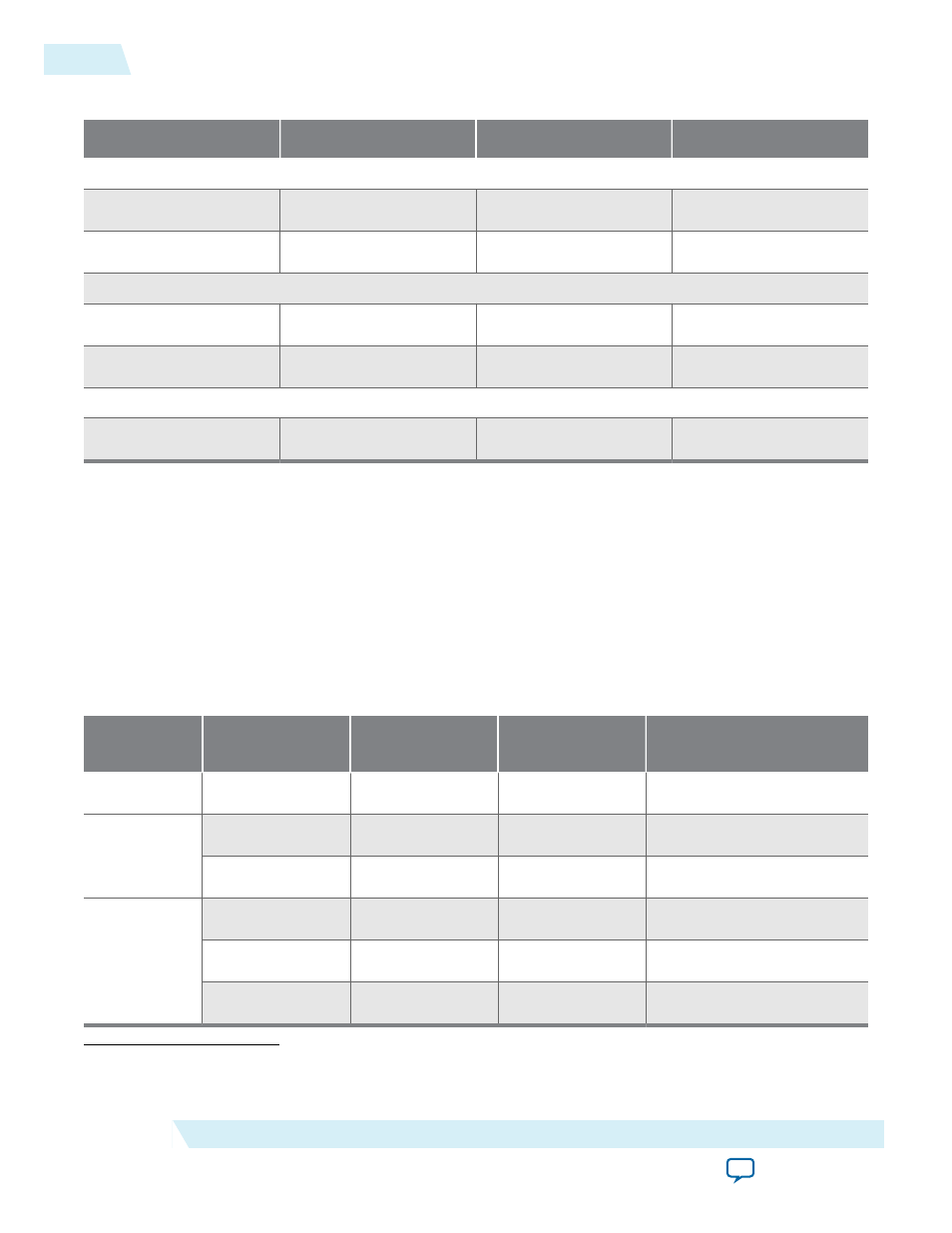

Table 1-5: Performance and Resource Utilization Avalon-MM Hard IP for PCI Express

Interface Width

ALMs

M20K Memory Blocks

Logic Registers

Avalon-MM Bridge

64

1100

17

1500

128

1900

25

2900

Avalon-MM Interface–Completer Only

64

650

8

1000

128

1400

12

2400

Avalon-MM–Completer Only Single Dword

64

250

0

350

Note: Soft calibration of the transceiver module requires additional logic. The amount of logic required

depends upon the configuration.

Related Information

Recommended Speed Grades

Table 1-6: Stratix V Recommended Speed Grades for All Avalon-MM Widths and Frequencies

Lane Rate

Link Width

Interface Width

Application Clock

Frequency (MHz)

Recommended Speed Grades

Gen1

×8

128 Bits

125

–1, –2, –3, –4

Gen2

×4

128 bits

125

–1, –2, –3, –4

×8

128 bits

250

–1, –2, –3

Gen3

×2

128 bits

125

–1, –2, –3

(2)

×4

128 bits

250

–1, –2, –3

(2)

×8

256 bits

250

–1, –2, –3

(2)

(2)

The -4 speed grade is also possible for this configuration; however, it requires significant effort by the end

user to close timing.

1-10

Recommended Speed Grades

UG-01097_avmm

2014.12.15

Altera Corporation

Datasheet