Altera Stratix V Avalon-MM Interface for PCIe Solutions User Manual

Page 52

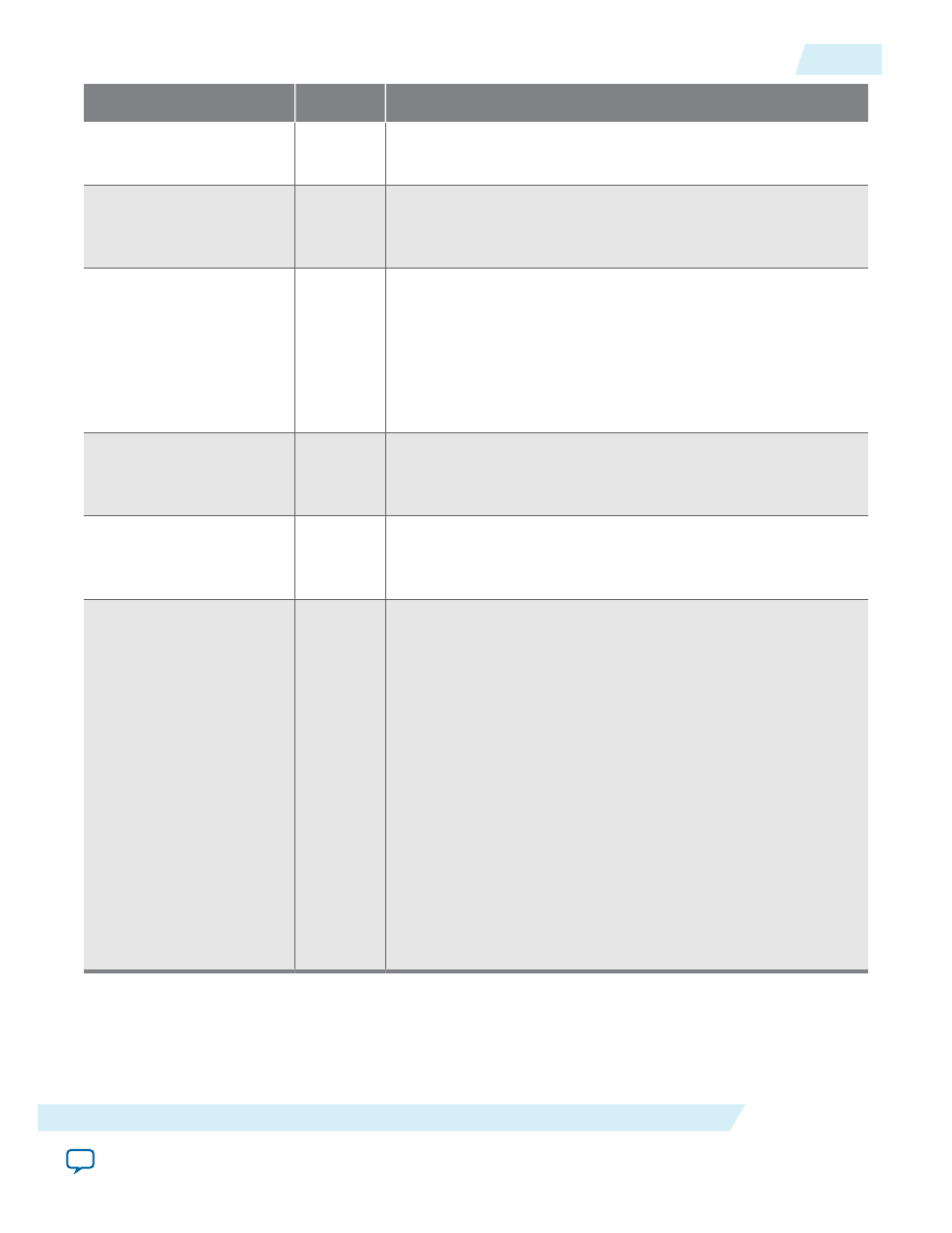

Signal

Direction

Description

rx_st_sop

Output

Indicates that this is the first cycle of the TLP when

rx_st_valid

is asserted.

rx_st_valid

Output

Clocks

rx_st_data

into the Application Layer. Deasserts within

2 clocks of

rx_st_ready

deassertion and reasserts within 2 clocks

of

rx_st_ready

assertion if more data is available to send.

serr_out

Output

System Error: This signal only applies to Root Port designs that

report each system error detected, assuming the proper enabling

bits are asserted in the Root Control and Device Control

registers. If enabled,

serr_out

is asserted for a single clock cycle

when a system error occurs. System errors are described in the

PCI Express Base Specification 2.1 or 3.0 in the Root Control

register.

tl_cfg_add[3:0]

Output

Address of the register that has been updated. This signal is an

index indicating which Configuration Space register information

is being driven onto

tl_cfg_ctl

.

tl_cfg_sts[52:0]

Output

Configuration status bits. This information updates every

pld_

clk

cycle. The following table provides detailed descriptions of

the status bits.

tx_st_ready

Output

Indicates that the Transaction Layer is ready to accept data for

transmission. The core deasserts this signal to throttle the data

stream.

tx_st_ready

may be asserted during reset. The Applica‐

tion Layer should wait at least 2 clock cycles after the reset is

released before issuing packets on the Avalon-ST TX interface.

The

reset_status

signal can also be used to monitor when the

IP core has come out of reset.

If asserted by the Transaction Layer on cycle

tx_st_ready

,

then

is a ready cycle, during which the

Application Layer may assert

tx_st_valid

and transfer data.

When

tx_st_ready

,

tx_st_valid

and

tx_st_data

are

registered (the typical case), Altera recommends a

readyLatency

of 2 cycles to facilitate timing closure; however, a

readyLatency

of 1 cycle is possible. If no other delays are added to the

read-valid latency, the resulting delay corresponds to a

readyLa-

tency

of 2.

UG-01097_avmm

2014.12.15

Hard IP Status Extension

4-19

64- or 128-Bit Avalon-MM Interface to the Application Layer

Altera Corporation