Physical layer interface signals, Transceiver reconfiguration – Altera Stratix V Avalon-MM Interface for PCIe Solutions User Manual

Page 48

Signal

Direction

Description

IntxAck_o

Output

This signal is the acknowledge for

IntxReq_i

. It is asserted for at

least one cycle either when either of the following events occur:

• The

Assert_INTA

message TLP has been transmitted in

response to the assertion of the

IntxReq_i

.

• The

Deassert_INTA

message TLP has been transmitted in

response to the deassertion of the

IntxReq_i

signal.

Refer to the timing diagrams below.

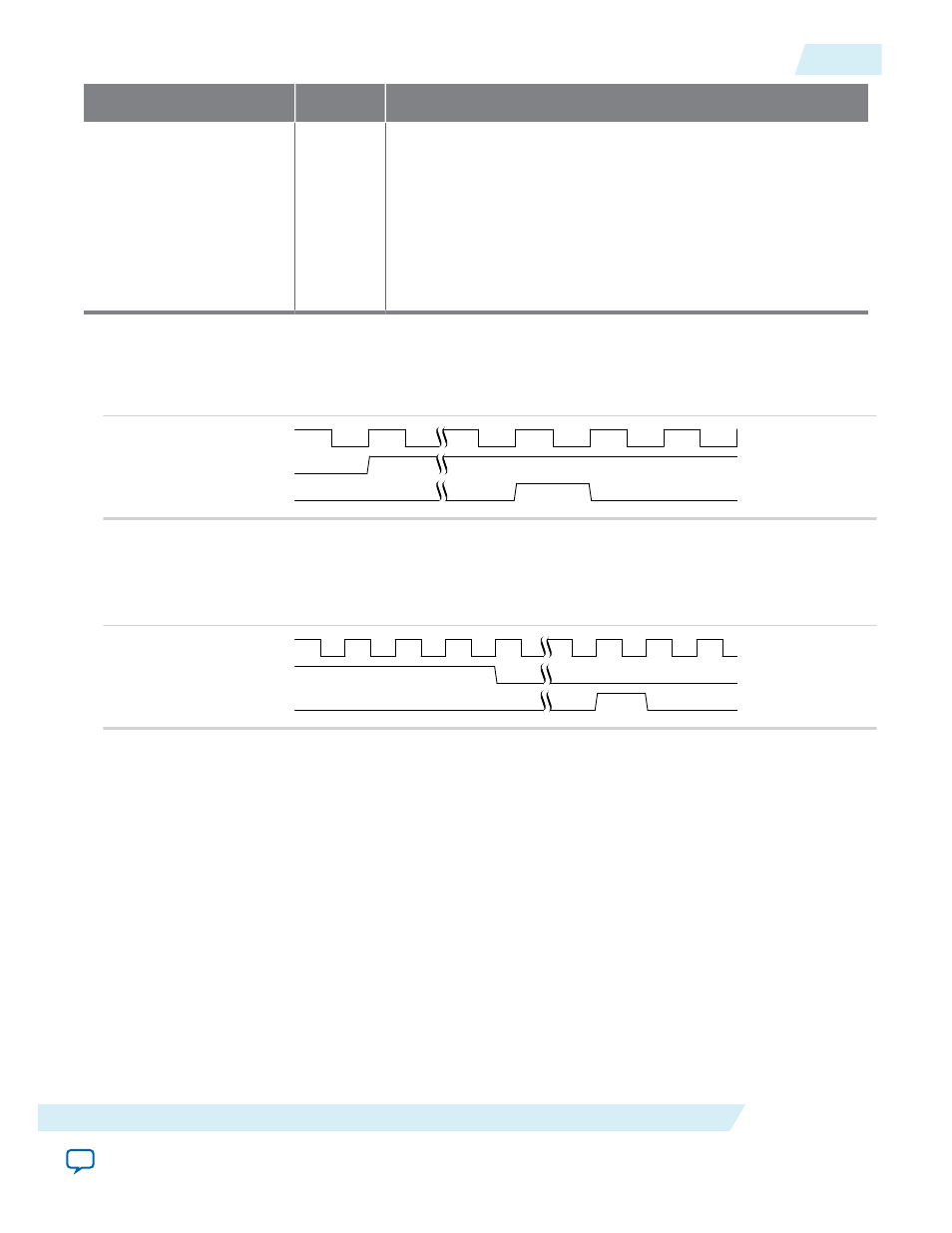

The following figure illustrates interrupt timing for the legacy interface. In this figure the assertion of

IntxReq_i

instructs the Hard IP for PCI Express to send an

Assert_INTA

message TLP.

Figure 4-4: Legacy Interrupt Assertion

clk

IntxReq_i

IntAck_o

The following figure illustrates the timing for deassertion of legacy interrupts. The assertion of

IntxReq_i

instructs the Hard IP for PCI Express to send a

Deassert_INTA

message.

Figure 4-5: Legacy Interrupt Deassertion

clk

IntxReq_i

IntAck_o

Physical Layer Interface Signals

Altera provides an integrated solution with the Transaction, Data Link and Physical Layers. The IP

Parameter Editor generates a SERDES variation file,

or .vhd , in addition to the Hard

IP variation file,

or

.vhd

. The SERDES entity is included in the library files for PCI Express.

Transceiver Reconfiguration

Dynamic reconfiguration compensates for variations due to process, voltage and temperature (PVT).

Among the analog settings that you can reconfigure are V

OD

, pre-emphasis, and equalization.

You can use the Altera Transceiver Reconfiguration Controller to dynamically reconfigure analog

settings. For more information about instantiating the Altera Transceiver Reconfiguration Controller IP

core refer to Hard IP Reconfiguration .

UG-01097_avmm

2014.12.15

Physical Layer Interface Signals

4-15

64- or 128-Bit Avalon-MM Interface to the Application Layer

Altera Corporation