Configuration space register access – Altera Stratix V Avalon-MM Interface for PCIe Solutions User Manual

Page 54

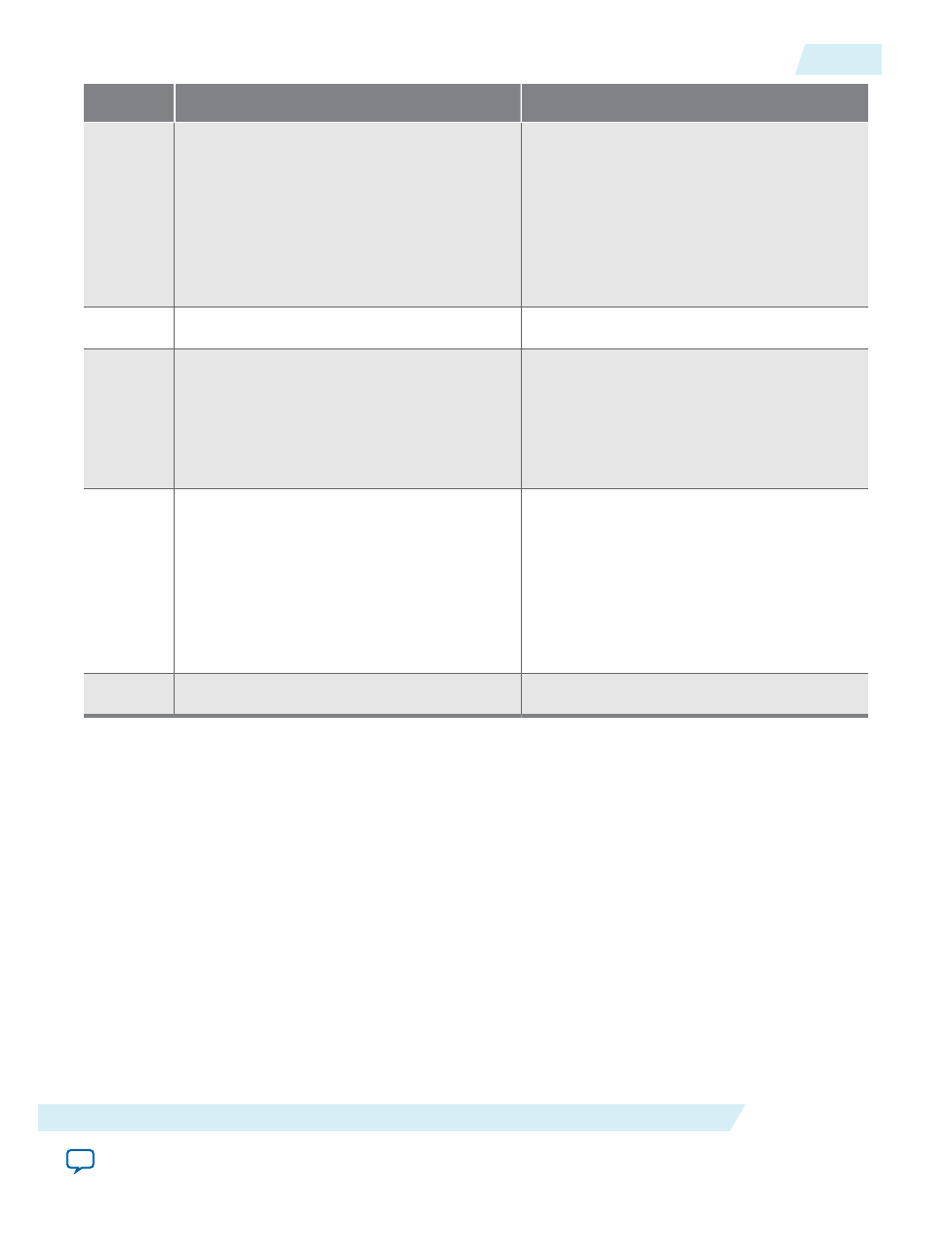

tl_cfg_sts

Configuration Space Register

Description

[29:25] Status Register[15:11]

Records the following 5 primary command

status errors:

• Bit 15: detected parity error

• Bit 14: signaled system error

• Bit 13: received master abort

• Bit 12: received target abort

• Bit 11: signalled target abort

[24]

Secondary Status Register[8]

Master data parity error

[23:6]

Root Status Register[17:0]

Records the following PME status informa‐

tion:

• Bit 17: PME pending

• Bit 16: PME status

• Bits[15:0]: PME request ID[15:0]

[5:1]

Secondary Status Register[15:11]

Records the following 5 secondary command

status errors:

• Bit 15: detected parity error

• Bit 14: received system error

• Bit 13: received master abort

• Bit 12: received target abort

• Bit 11: signalled target abort

[0]

Secondary Status Register[8]

Master Data Parity Error

Related Information

Configuration Space Register Access

The

tl_cfg_ctl

signal is a multiplexed bus that contains the contents of Configuration Space registers as

shown in the figure below. Information stored in the Configuration Space is accessed in round robin

order where

tl_cfg_add

indicates which register is being accessed. The following table shows the layout

of configuration information that is multiplexed on

tl_cfg_ctl

.

UG-01097_avmm

2014.12.15

Configuration Space Register Access

4-21

64- or 128-Bit Avalon-MM Interface to the Application Layer

Altera Corporation