Features – Altera Stratix V Avalon-MM Interface for PCIe Solutions User Manual

Page 3

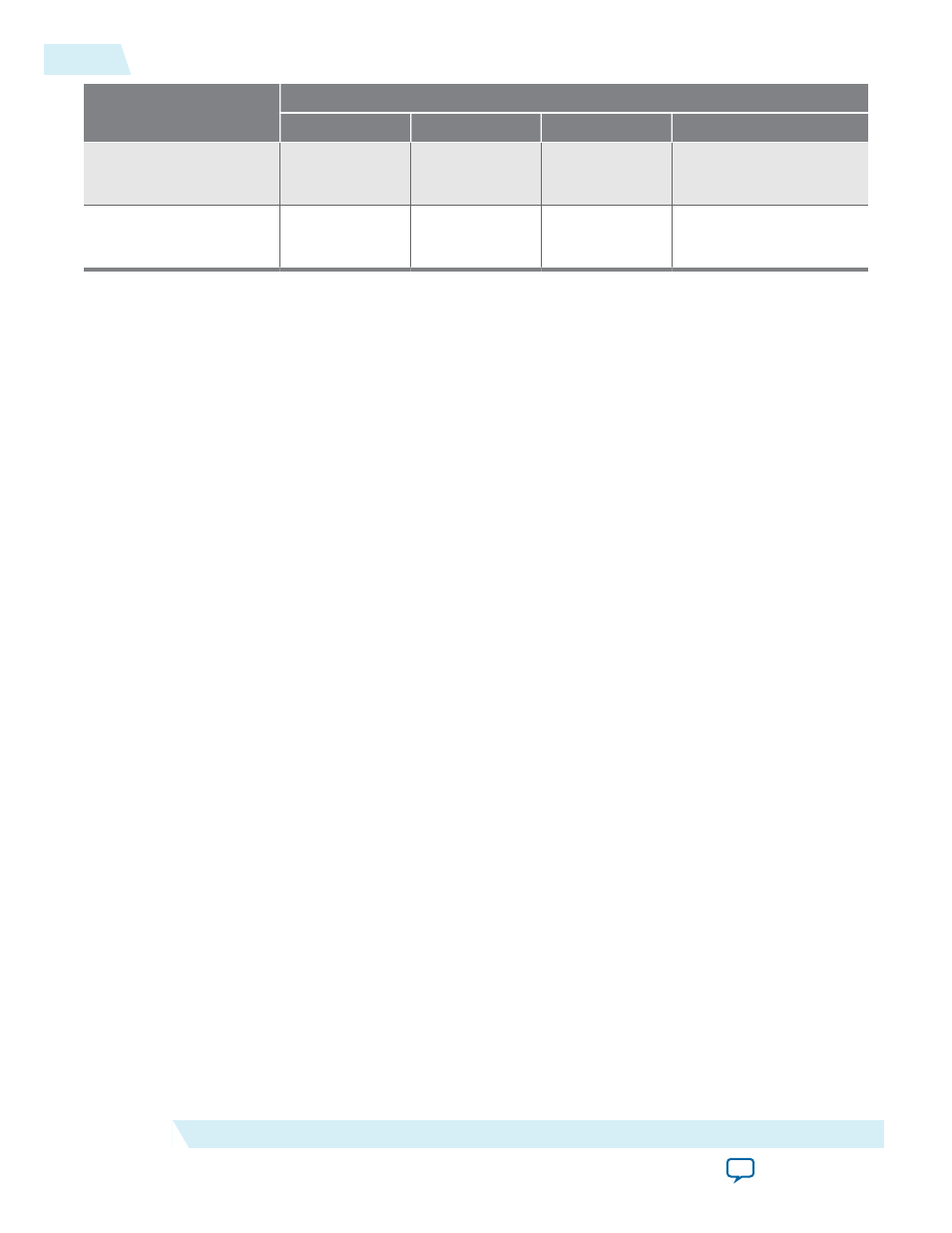

Link Width in Gigabits Per Second (Gbps)

x1

x2

x4

x8

PCI Express Gen2

(5.0 Gbps)

4

8

16

32

PCI Express Gen3

(8.0 Gbps)

7.87

15.75

31.51

63

Refer to the PCI Express Reference Design for Stratix V Devices for more information about calculating

bandwidth for the hard IP implementation of PCI Express in many Altera FPGAs, including the Stratix V

Hard IP for PCI Express IP core.

Related Information

•

•

•

Features

New features in the Quartus

®

II 14.1 software release:

• Reduced Quartus II compilation warnings by 50%.

The Stratix V Hard IP for PCI Express with the Avalon-MM interface supports the following features:

• Complete protocol stack including the Transaction, Data Link, and Physical Layers implemented as

hard IP.

• Support for ×1, ×2, ×4, and ×8 configurations with Gen1, Gen2, or Gen3 lane rates for Root Ports and

Endpoints.

• Dedicated 16 KByte receive buffer.

• Optional hard reset controller for Gen2.

• Optional support for Configuration via Protocol (CvP) using the PCIe link allowing the I/O and core

bitstreams to be stored separately.

• Support for 32- or 64-bit addressing for the Avalon-MM interface to the Application Layer.

• Qsys example designs demonstrating parameterization, design modules, and connectivity.

• Extended credit allocation settings to better optimize the RX buffer space based on application type.

• Optional end-to-end cyclic redundancy code (ECRC) generation and checking and advanced error

reporting (AER) for high reliability applications.

• Support for Configuration Space Bypass Mode, allowing you to design a custom Configuration Space

and support multiple functions.

• Support for Gen3 PIPE simulation.

• Easy to use:

• Flexible configuration.

• No license requirement.

• Example designs to get started.

1-2

Features

UG-01097_avmm

2014.12.15

Altera Corporation

Datasheet