Or 128-bit bursting tx avalon-mm slave signals – Altera Stratix V Avalon-MM Interface for PCIe Solutions User Manual

Page 38

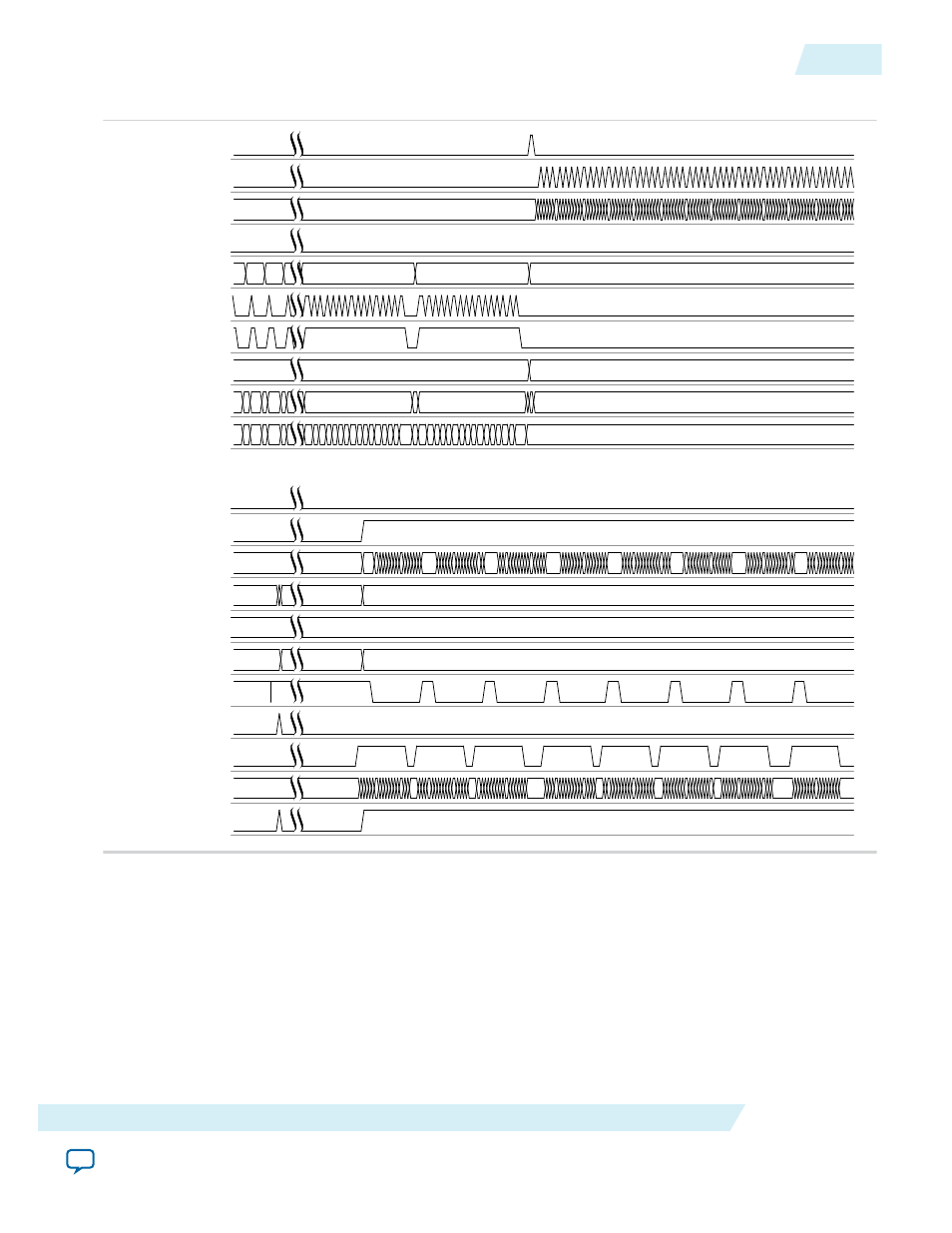

Figure 4-2: Simultaneous DMA Read, DMA Write, and Target Access

RxmRead_o

RxmReadDataValid_i

RxmReadData_i[63:0]

RxmResetRequest_o

RxmAddress_o[31:0]

RxmWaitRequest_i

RxmWrite_o

RxmBurstCount_o[9:0]

RxmByteEnable_o[7:0]

RxmWriteData_o[63:0]

RxmIrq_i

TxsWrite_i

TxsWriteData_i[63:0]

TxsBurstCount_i[9:0]

TxsByteEnable_i[7:0]

TxsAddress_i[17:0]

TxsWaitRequest_o

TxsRead_i

TxsReadDataValid_o

TxsReadData_o[63:0]

TxsChipSelect_i

..

.

. .

80000100

80000180

010

.

FF

FF

.

.

000000000002080F

.

.

.

.

.

.

.

001

080

04000

04080

04000

00000

.

.

0 .

64- or 128-Bit Bursting TX Avalon-MM Slave Signals

This optional Avalon-MM bursting slave port propagates requests from the interconnect fabric to the full-

featured Avalon-MM Stratix V Hard IP for PCI Express. Requests from the interconnect fabric are

translated into PCI Express request packets. Incoming requests can be up to 512 bytes. For better

performance, Altera recommends using smaller read request size (a maximum of 512 bytes).

UG-01097_avmm

2014.12.15

64- or 128-Bit Bursting TX Avalon-MM Slave Signals

4-5

64- or 128-Bit Avalon-MM Interface to the Application Layer

Altera Corporation