Altera Stratix V Avalon-MM Interface for PCIe Solutions User Manual

Page 5

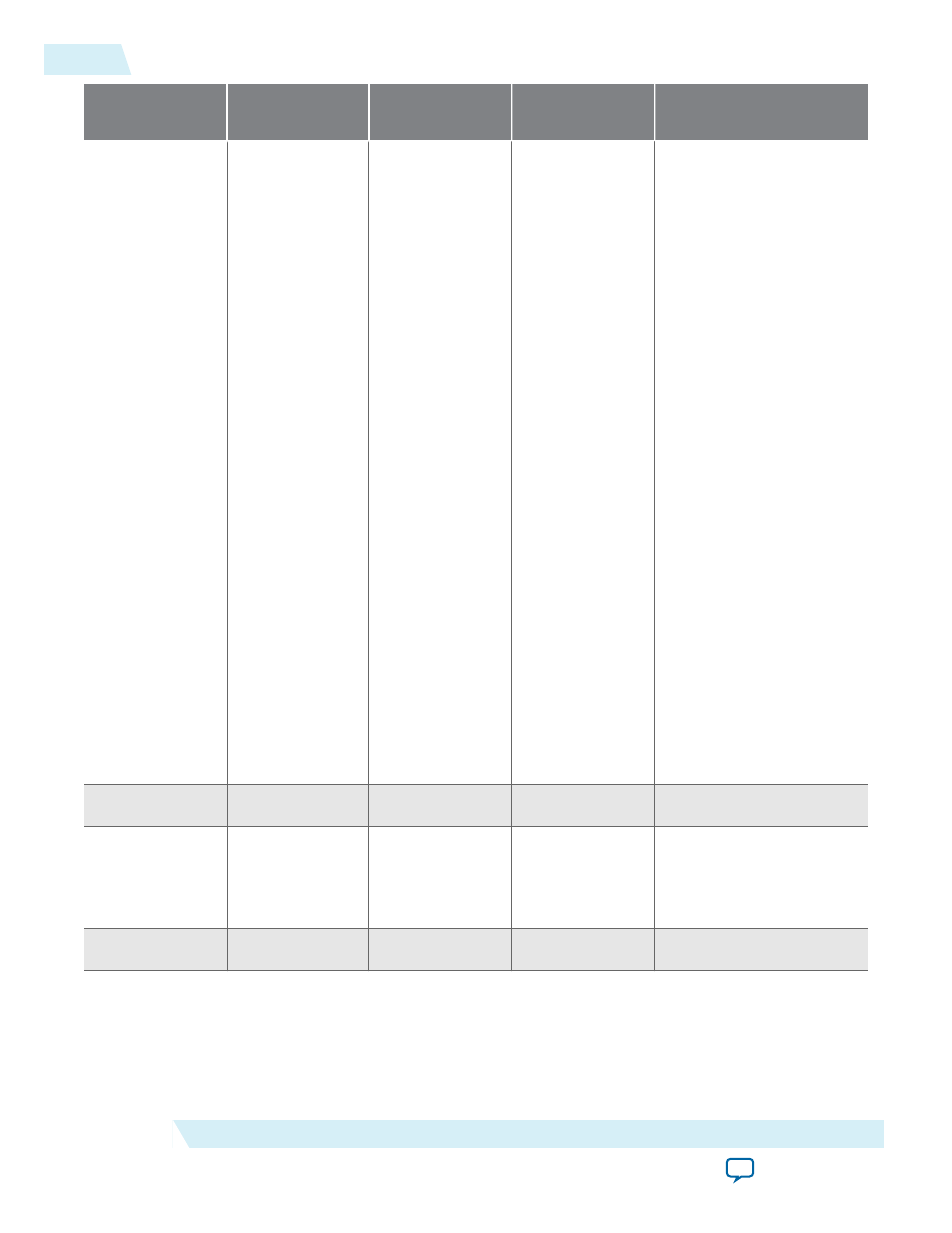

Feature

Avalon‑ST Interface

Avalon‑MM

Interface

Avalon‑MM DMA

Avalon‑ST Interface with SR-

IOV

Transaction

Layer Packet

type (TLP)

• Memory Read

Request

• Memory Read

Request-

Locked

• Memory Write

Request

• I/O Read

Request

• I/O Write

Request

• Configuration

Read Request

(Root Port)

• Configuration

Write Request

(Root Port)

• Message

Request

• Message

Request with

Data Payload

• Completion

Message

• Completion

with Data

• Completion for

Locked Read

without Data

• Memory Read

Request

• Memory Write

Request

• I/O Read

Request—Root

Port only

• I/O Write

Request—Root

Port only

• Configuration

Read Request

(Root Port)

• Configuration

Write Request

(Root Port)

• Completion

Message

• Completion

with Data

• Memory Read

Request (single

dword)

• Memory Write

Request (single

dword)

• Memory Read

Request

• Memory Write

Request

• Completion

Message

• Completion

with Data

• Memory Read Request

• Memory Write

Request

• Configuration Read

Request (from Root

Port)

• Configuration Write

Request (from Root

Port)

• Message Request

• Completion Message

• Completion with Data

Payload size

128–2048 bytes

128–256 bytes

128, 256, 512 bytes 128–256 bytes

Number of tags

supported for

non-posted

requests

256

8

16

256

62.5 MHz clock Supported

Supported

Not Supported

Not Supported

1-4

Features

UG-01097_avmm

2014.12.15

Altera Corporation

Datasheet