Altera Stratix V Avalon-MM Interface for PCIe Solutions User Manual

Page 156

a. Double-click in the Assignment Name column and scroll to the bottom of the available

assignments.

b. Select VCCA_GXB Voltage.

c. In the Value column, select 3_0V from the list.

The Quartus II software adds these instance assignments commands to the

.qsf

file for your project.

You can also enter these commands at the Quartus II Tcl Console. For example, the following command

sets the

XCVR_VCCR_VCCT_VOLTAGE

to 1.0 V for the pin specified:

set_instance_assignment -name XCVR_VCCR_VCCT_VOLTAGE 1_0V to “pin”

Related Information

•

•

Recommended Reset Sequence to Avoid Link Training Issues

Successful link training can only occur after the FPGA is configured and the Transceiver Reconfiguration

Controller IP Core has dynamically reconfigured SERDES analog settings to optimize signal quality. For

designs using CvP, link training occurs after configuration of the I/O ring and Hard IP for PCI Express IP

Core. Refer to Reset Sequence for Hard IP for PCI Express IP Core and Application Layer for a description

of the key signals that control reset, control dynamic reconfiguration, and link training. Altera

recommends separate control of reset signals for the Endpoint and Root Port. Successful reset sequence

includes the following steps:

1. Wait until the FPGA is configured as indicated by the assertion of

CONFIG_DONE

from the FPGA block

controller.

2. Deassert the

mgmt_rst_reset

input to the Transceiver Reconfiguration Controller IP Core.

3. Wait for

tx_cal_busy

and

rx_cal_busy

SERDES outputs to be deasserted.

4. Wait 1 ms after the assertion of

CONFIG_DONE

, then deassert the Endpoint reset.

5. Wait approximately 100 ms, then deassert the Root Port reset.

6. Deassert the reset output to the Application Layer.

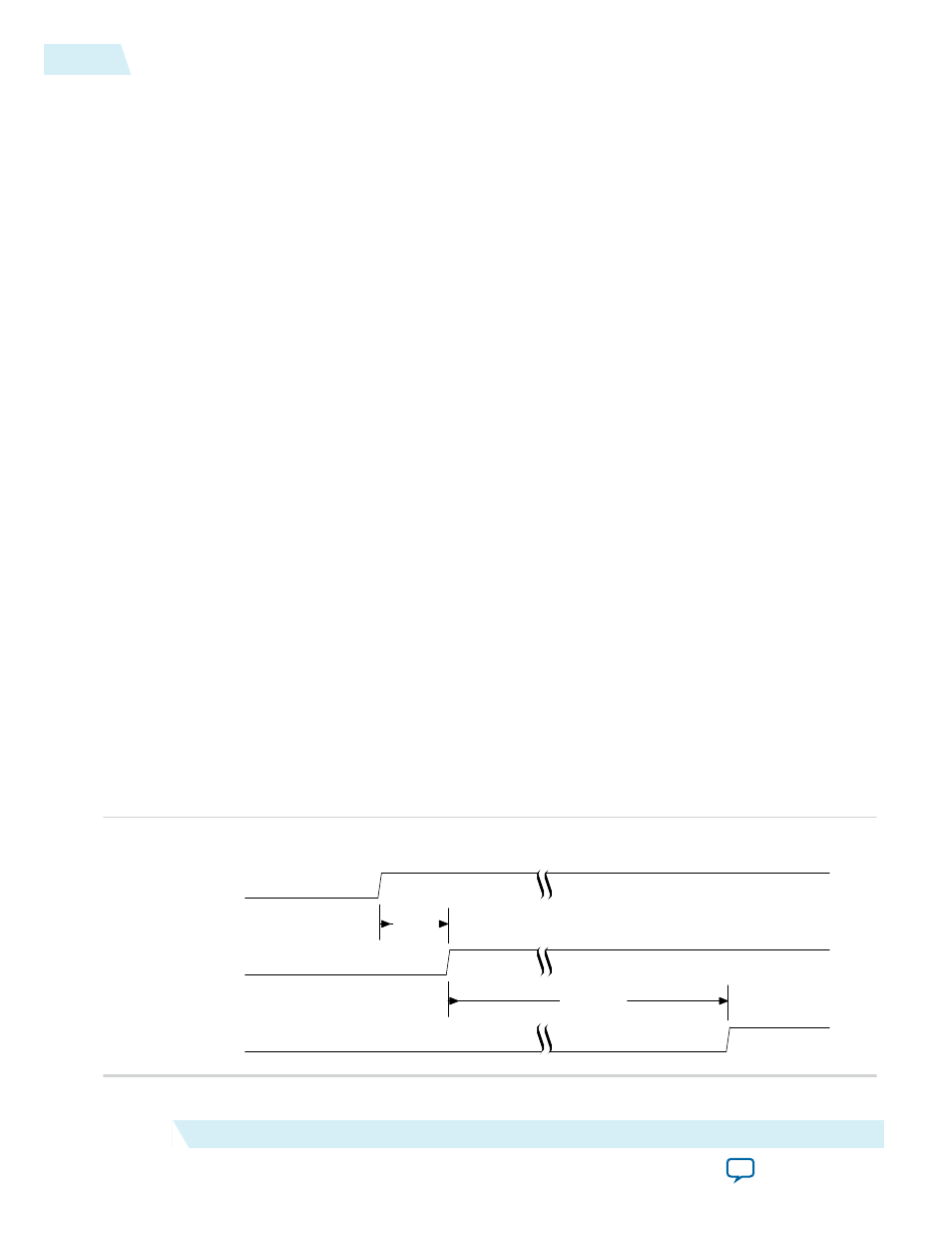

Figure 12-1: Recommended Reset Sequence

CONF_DONE

Endpoint Reset

Root Port Reset

1 ms

100 ms

12-2

Recommended Reset Sequence to Avoid Link Training Issues

UG-01097_avmm

2014.12.15

Altera Corporation

Design Implementation