Altera Stratix V Avalon-MM Interface for PCIe Solutions User Manual

Page 45

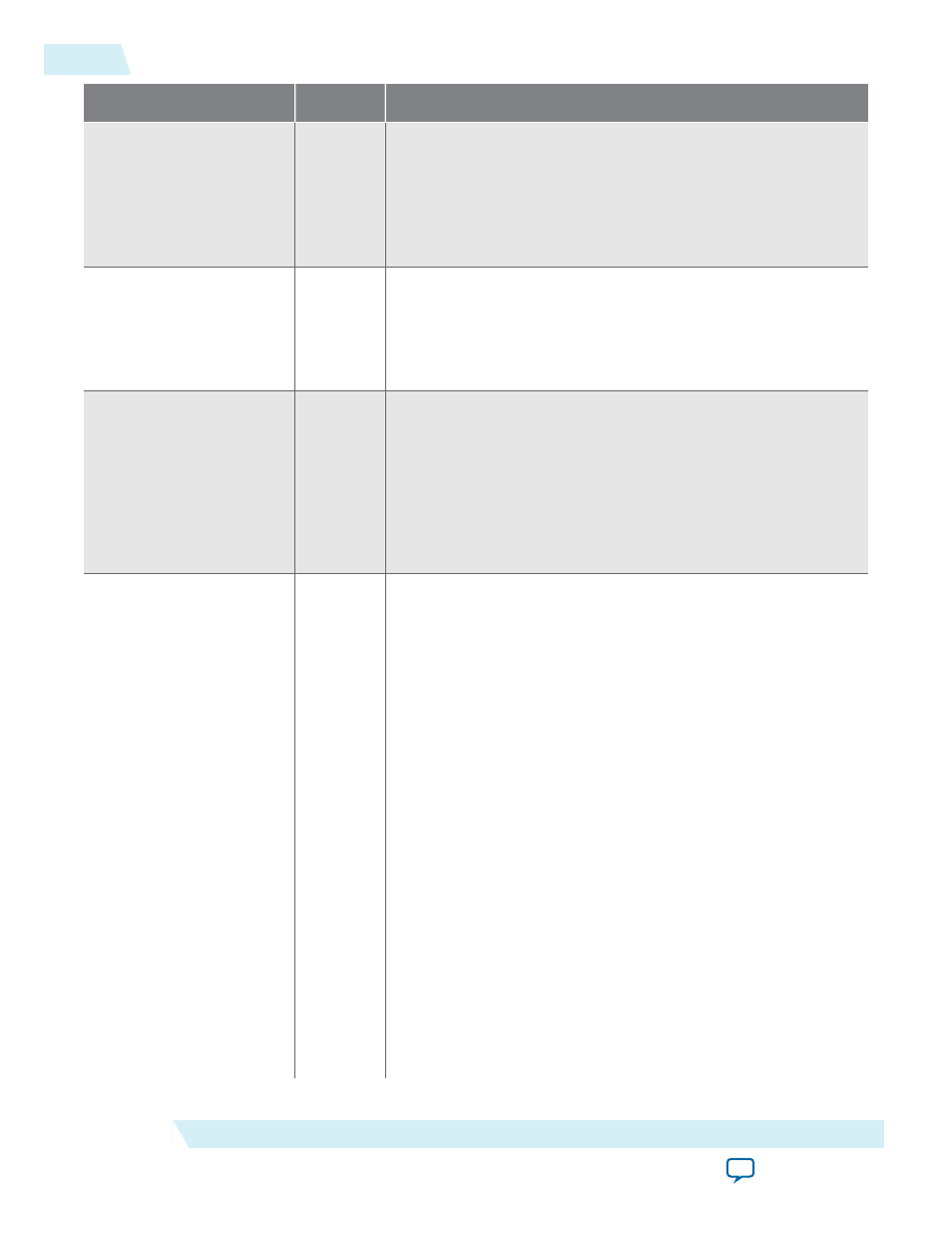

Signal

Direction

Description

ko_cpl_spc_

header[7:0]

Output

The Application Layer can use this signal to build circuitry to

prevent RX buffer overflow for completion headers. Endpoints

must advertise infinite space for completion headers; however,

RX buffer space is finite.

ko_cpl_spc_header

is a static signal

that indicates the total number of completion headers that can be

stored in the RX buffer.

l2_exit

Output

L2 exit. This signal is active low and otherwise remains high. It is

asserted for one cycle (changing value from 1 to 0 and back to 1)

after the LTSSM transitions from l2.idle to detect. When this

pulse is asserted, the Application Layer should generate an

internal reset signal that is asserted for at least 32 cycles.

lane_act[3:0]

Output

Lane Active Mode: This signal indicates the number of lanes that

configured during link training. The following encodings are

defined:

• 4’b0001: 1 lane

• 4’b0010: 2 lanes

• 4’b0100: 4 lanes

• 4’b1000: 8 lanes

ltssmstate[4:0]

Output

LTSSM state: The LTSSM state machine encoding defines the

following states:

• 00000: Detect.Quiet

• 00001: Detect.Active

• 00010: Polling.Active

• 00011: Polling.Compliance

• 00100: Polling.Configuration

• 00101: Polling.Speed

• 00110: config.Linkwidthstart

• 00111: Config.Linkaccept

• 01000: Config.Lanenumaccept

• 01001: Config.Lanenumwait

• 01010: Config.Complete

• 01011: Config.Idle

• 01100: Recovery.Rcvlock

• 01101: Recovery.Rcvconfig

• 01110: Recovery.Idle

• 01111: L0

• 10000: Disable

• 10001: Loopback.Entry

• 10010: Loopback.Active

4-12

Reset

UG-01097_avmm

2014.12.15

Altera Corporation

64- or 128-Bit Avalon-MM Interface to the Application Layer