Altera Stratix V Avalon-MM Interface for PCIe Solutions User Manual

Page 47

Interrupts for Endpoints when Multiple MSI/MSI‑X Support Is Enabled

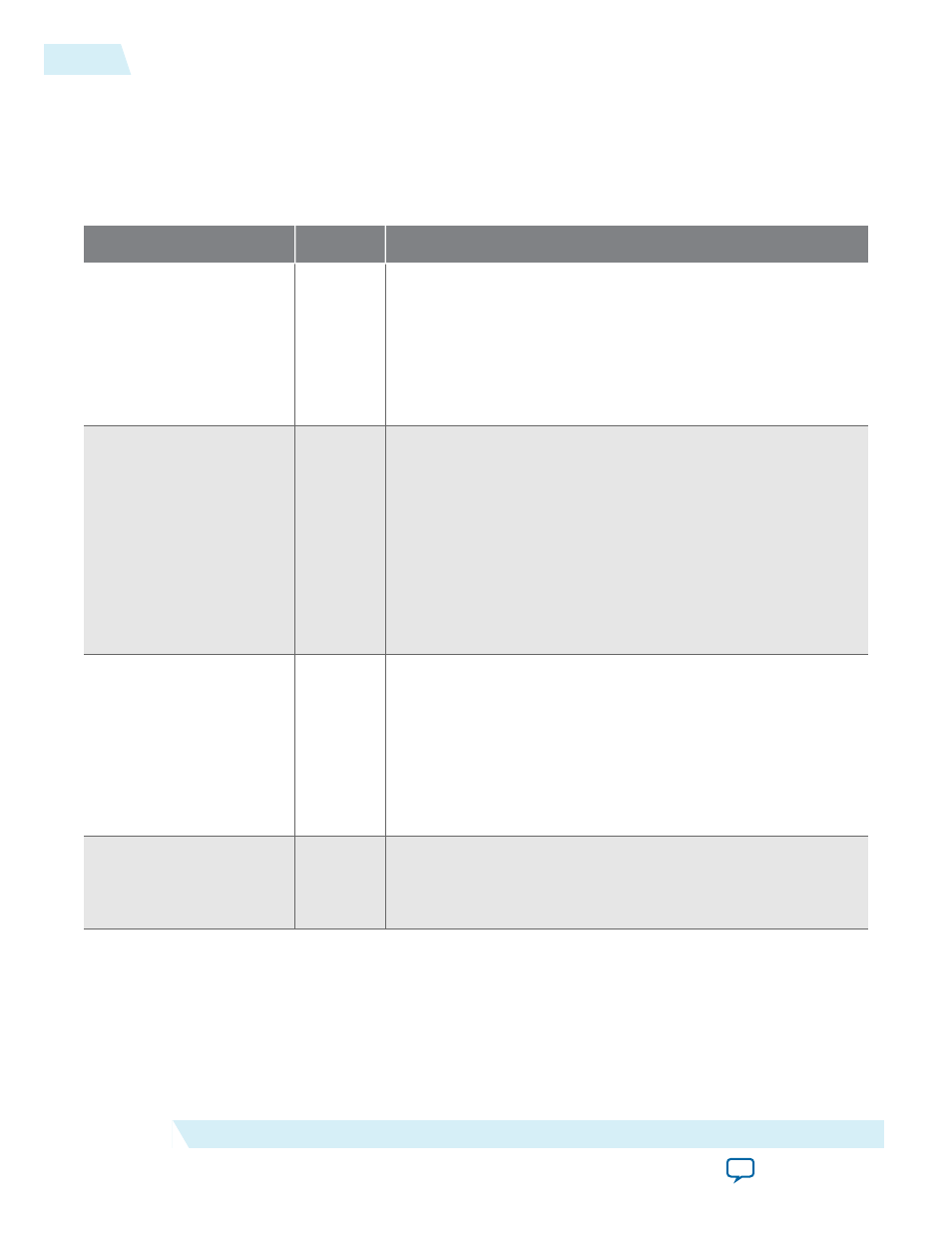

Table 4-7: Exported Interrupt Signals for Endpoints when Multiple MSI/MSI‑X Support is Enabled

The following table describes the IP core’s exported interrupt signals when you turn on Enable multiple MSI/

MSI-X support under the Avalon-MM System Settings banner in the parameter editor.

Signal

Direction

Description

MsiIntfc_o[81:0]

Output

This bus provides the following MSI address, data, and enabled

signals:

•

MsiIntf_o[81]

: Master enable

•

MsiIntf_o[80

}: MSI enable

•

MsiIntf_o[79:64]

: MSI data

•

MsiIntf_o[63:0]

: MSI address

MsiControl_o[15:0]

Output

Provides for system software control of MSI as defined in Section

6.8.1.3 Message Control for MSI in the PCI Local Bus Specifica‐

tion, Rev. 3.0. The following fields are defined:

•

MsiControl_o[15:9]

: Reserved

•

MsiControl_o[8]

: Per-vector masking capable

•

MsiControl_o[7]

: 64-bit address capable

•

MsiControl_o[6:4]

: Multiple Message Enable

•

MsiControl_o[3:1]

: MSI Message Capable

•

MsiControl_o[0]

: MSI Enable.

MsixIntfc_o[15:0]

Output

Provides for system software control of MSI-X as defined in

Section 6.8.2.3 Message Control for MSI-X in the PCI Local Bus

Specification, Rev. 3.0. The following fields are defined:

•

MsixIntfc_o[15]

: Enable

•

MsixIntfc_o[14]

: Mask

•

MsixIntfc_o[13:11]

: Reserved

•

MsixIntfc_o[10:0]

: Table size

IntxReq_i

Input

When asserted, the Endpoint is requesting attention from the

interrupt service routine unless MSI or MSI-X interrupts are

enabled. Remains asserted until the device driver clears the

pending request.

4-14

Interrupts for Endpoints when Multiple MSI/MSI‑X Support Is Enabled

UG-01097_avmm

2014.12.15

Altera Corporation

64- or 128-Bit Avalon-MM Interface to the Application Layer