Pci express and pci capabilities parameters, Device capabilities – Altera Stratix V Avalon-MM Interface for PCIe Solutions User Manual

Page 25

Related Information

PCI Express and PCI Capabilities Parameters

This group of parameters defines various capability properties of the IP core. Some of these parameters

are stored in the PCI Configuration Space - PCI Compatible Configuration Space. The byte offset

indicates the parameter address.

Device Capabilities

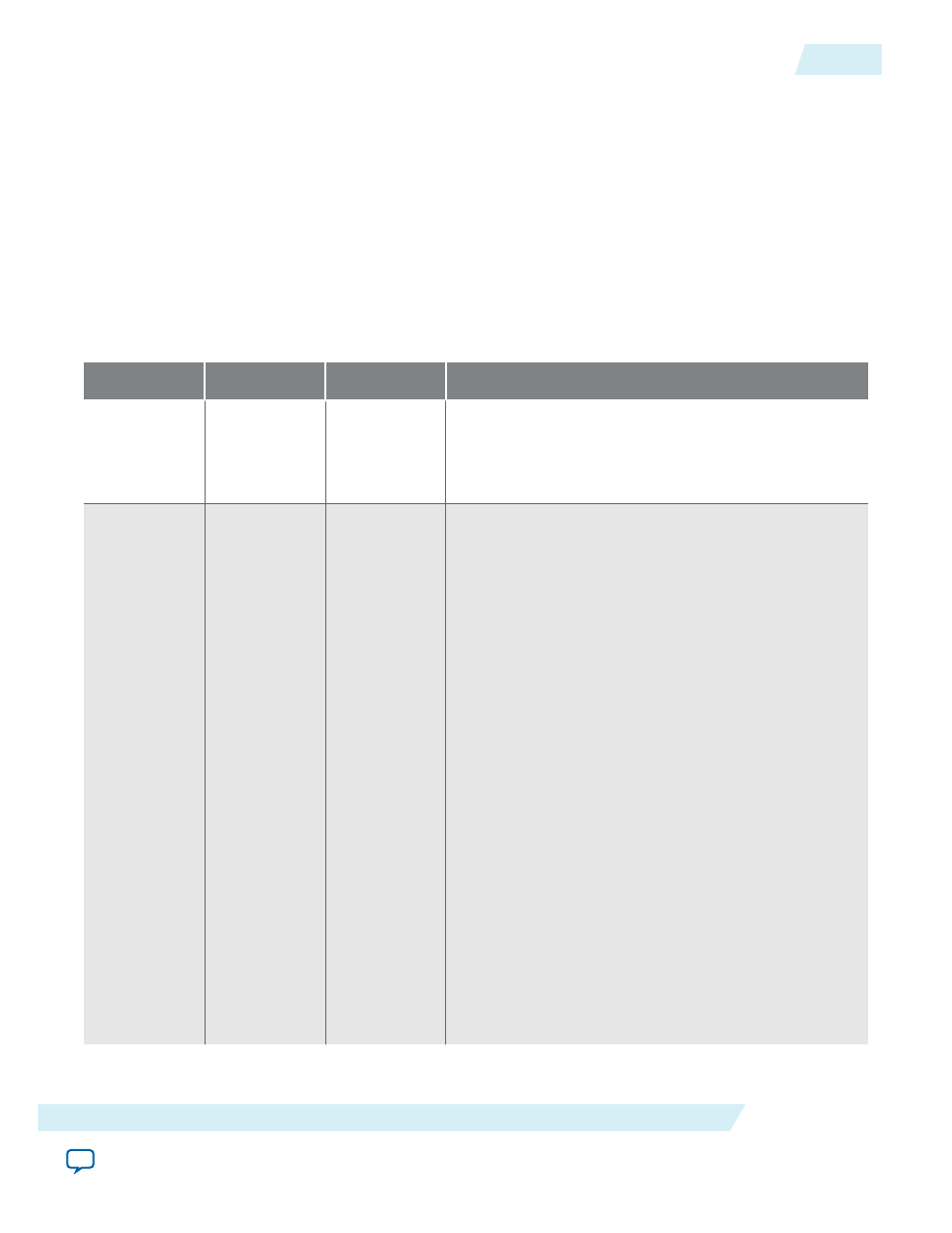

Table 3-4: Capabilities Registers

Parameter

Possible Values

Default Value

Description

Maximum

payload size

128 bytes

256 bytes

128 bytes

Specifies the maximum payload size supported. This

parameter sets the read-only value of the max payload

size supported field of the Device Capabilities register

(0x084[2:0]). Address: 0x084.

Completion

timeout

range

ABCD

BCD

ABC

AB

B

A

None

ABCD

Indicates device function support for the optional

completion timeout programmability mechanism. This

mechanism allows the system software to modify the

completion timeout value. This field is applicable only to

Root Ports and Endpoints that issue requests on their

own behalf. Completion timeouts are specified and

enabled in the Device Control 2 register (0x0A8) of the

PCI Express Capability Structure Version. For all other

functions this field is reserved and must be hardwired to

0x0000b. Four time value ranges are defined:

• Range A: 50 us to 10 ms

• Range B: 10 ms to 250 ms

• Range C: 250 ms to 4 s

• Range D: 4 s to 64 s

Bits are set to show timeout value ranges supported. The

function must implement a timeout value in the range

50 sto 50 ms. The following values specify the range:

• None—Completion timeout programming is not

supported

• 0001 Range A

• 0010 Range B

• 0011 Ranges A and B

• 0110 Ranges B and C

UG-01097_avmm

2014.12.15

PCI Express and PCI Capabilities Parameters

3-5

Parameter Settings

Altera Corporation