3 external reset, 4 watchdog reset, 5 black-out detection – Rainbow Electronics ATmega8HVD User Manual

Page 40: Atmega4hvd/8hvd

40

8052B–AVR–09/08

ATmega4HVD/8HVD

10.3

External Reset

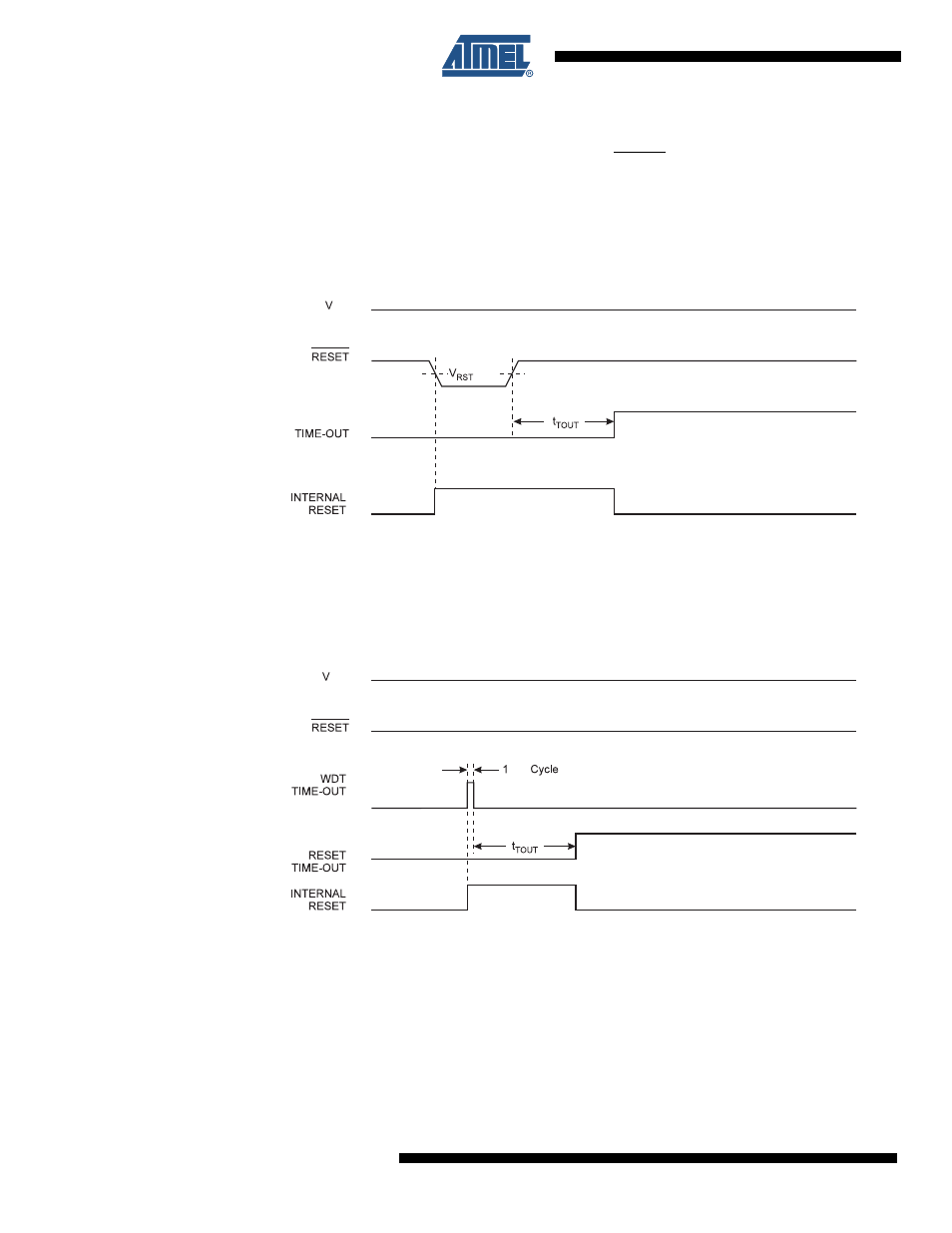

An External Reset is generated by a low level on the RESET pin. Reset pulses longer than the

minimum pulse width (see

”System and Reset Characteristics” on page 144

) will generate a

reset, even if the clock is not running. Shorter pulses are not guaranteed to generate a reset.

When the applied signal reaches the Reset Threshold Voltage, V

RST

, on its positive edge, the

delay counter starts the MCU after the timeout period, t

TOUT

, has expired.

Figure 10-2. External Reset During Operation

10.4

Watchdog Reset

When the Watchdog times out, it will generate a short reset pulse of one CK cycle duration.

On the falling edge of this pulse, the delay timer starts counting the timeout period t

TOUT

. Refer

to

page 38

for details on operation of the Watchdog Timer.

Figure 10-3. Watchdog Reset During Operation

10.5

Black-out Detection

ATmega4HVD/8HVD has an on-chip Black-out Detection (BLOD) circuit for monitoring the

VREG level during operation by comparing it to a trigger level defined by hardware.

The ATmega4HVD/8HVD has two detection levels and two application areas for BLOD, see

”System and Reset Characteristics” on page 144

. One detection level (V

BLOT, START-UP

) is used

to ensure that the voltage on VFET is sufficient to operate the voltage regulator within its spec-

ifications when the chip starts up. The other detection level is used during normal operation

(V

BLOT, NORMAL

) to determine if VREG drops below a voltage where correct operation cannot be

FET

CK

FET