2 prr0 – power reduction register 0, Atmega4hvd/8hvd – Rainbow Electronics ATmega8HVD User Manual

Page 37

37

8052B–AVR–09/08

ATmega4HVD/8HVD

• Bit 0 – SE: Sleep Enable

The SE bit must be written to logic one to make the MCU enter the sleep mode when the

SLEEP instruction is executed. To avoid the MCU entering the sleep mode unless it is the pro-

grammer’s purpose, it is recommended to write the Sleep Enable (SE) bit to one just before

the execution of the SLEEP instruction and to clear it immediately after waking up.

9.8.2

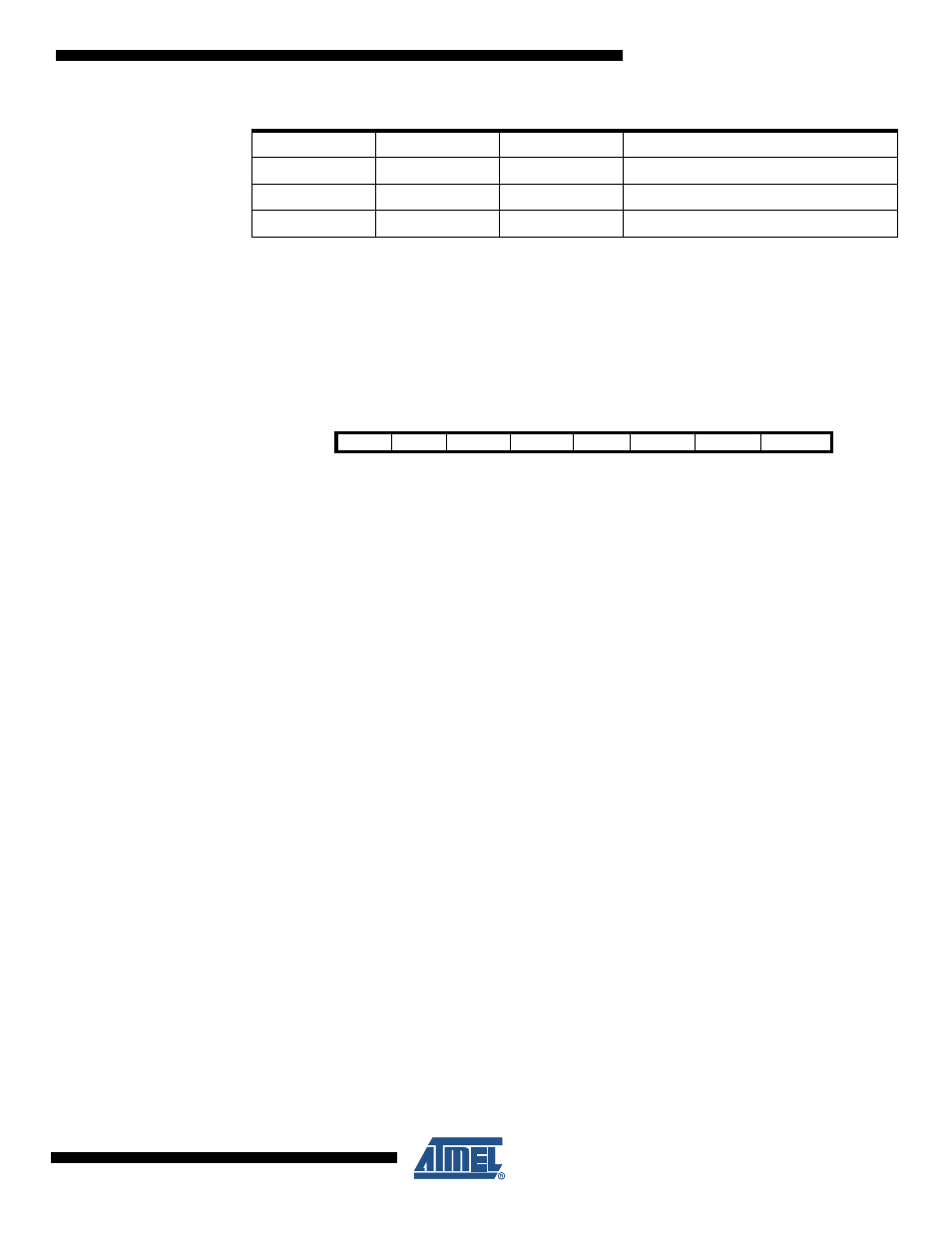

PRR0 – Power Reduction Register 0

• Bit 7:6 - Res: Reserved bits

These bits are reserved for future use. For compatibility with future devices, these bits must be

written to zero when PRR0 is written.

• Bit 5 - PRVRM: Power Reduction Voltage Regulator Monitor

Writing a logic one to this bit shuts down the Voltage Regulator Monitor interface by stopping

the clock of the module.

• Bit 4 - Res: Reserved bits

This bit is reserved for future use. For compatibility with future devices, this bit must be written

to zero when PRR0 is written.

• Bit 3 - PRSPI: Power Reduction Serial Peripheral Interface

Writing a logic one to this bit shuts down the Serial Periperal Interface by stopping the clock to

the module.

• Bit 2 - PRTIM1: Power Reduction Timer/Counter1

Writing a logic one to this bit shuts down the Timer/Counter1 module. When the

Timer/Counter1 is enabled, operation will continue like before the shutdown.

• Bit 1 - PRTIM0: Power Reduction Timer/Counter0

Writing a logic one to this bit shuts down the Timer/Counter0 module. When the

Timer/Counter0 is enabled, operation will continue like before the shutdown.

• Bit 0 - PRADC: Power Reduction ADC

Writing a logic one to this bit shuts down the ADC. Before writing the PRADC bit, make sure

that the ADEN bit is cleared to minimize the power consumption.

Note:

ADC control registers can be updated even if the PRADC bit is set.

1

0

1

Reserved

1

1

0

Reserved

1

1

1

Reserved

Table 9-3.

Sleep Mode Select (Continued)

SM2

SM1

SM0

Sleep Mode

Bit

7

6

5

4

3

2

1

0

-

-

PRVRM

-

PRSPI

PRTIM1

PRTIM0

PRADC

PRR0

Read/Write

R

R

R/W

R

R

R/W

R/W

R/W

Initial Value

0

0

0

0

0

0

0

0