4 register description, 1 fcsr – fet control and status register, Atmega4hvd/8hvd – Rainbow Electronics ATmega8HVD User Manual

Page 117

117

8052B–AVR–09/08

ATmega4HVD/8HVD

21.3

DUVR – Deep Under-Voltage Recovery Mode operation

The purpose of DUVR mode is to control the Charge FET so that the VFET voltage is above

the minimum operating voltage while charging cells below minimum operating voltage. This is

useful when the cell has been discharged below the minimum operating voltage of the chip. In

DUVR mode the Charge FET is switched partly on to provide a suitable voltage drop between

the cell voltage and the VFET terminal. As the cell voltage increases, the voltage drop across

the Charge FET will gradually decrease until the Charge FET is switched completely on. This

means that for high cell voltages, DUVR mode operation is equivalent to normal enabling of

the Charge FET (CFE=1).

ATmega4HVD/8HVD should operate in DUVR mode until software detects that the cell has

recovered from Deep Under-Voltage condition. When the cell has recovered from Deep

Under-Voltage condition, software should first set CFE=1. This is safe now since the cell volt-

age is above minimum operating voltage. After that software should disable DUVR mode by

setting DUVRD = 1.

If both DUVRD and CFE bit is set before the cell voltage is above minimum operating voltage,

the VFET voltage will drop and the chip will enter BLOD reset and switch off both the Charge-

and Discharge FET.

DUVR mode is default enabled after reset. However, while the chip is in reset state, DUVR

mode is disabled. This is a safety feature that ensures that the Charge FET will not be

switched on until the Charge Over-current Protection is operating. This implies that the DUVR

mode will be disabled from the time that a charger is connected until the selected start-up time

expired. During this period, the VFET voltage will be higher than the normal VFET Level in

DUVR mode.

For more details about DUVR mode, refer to application note AVR354.

21.4

Register Description

21.4.1

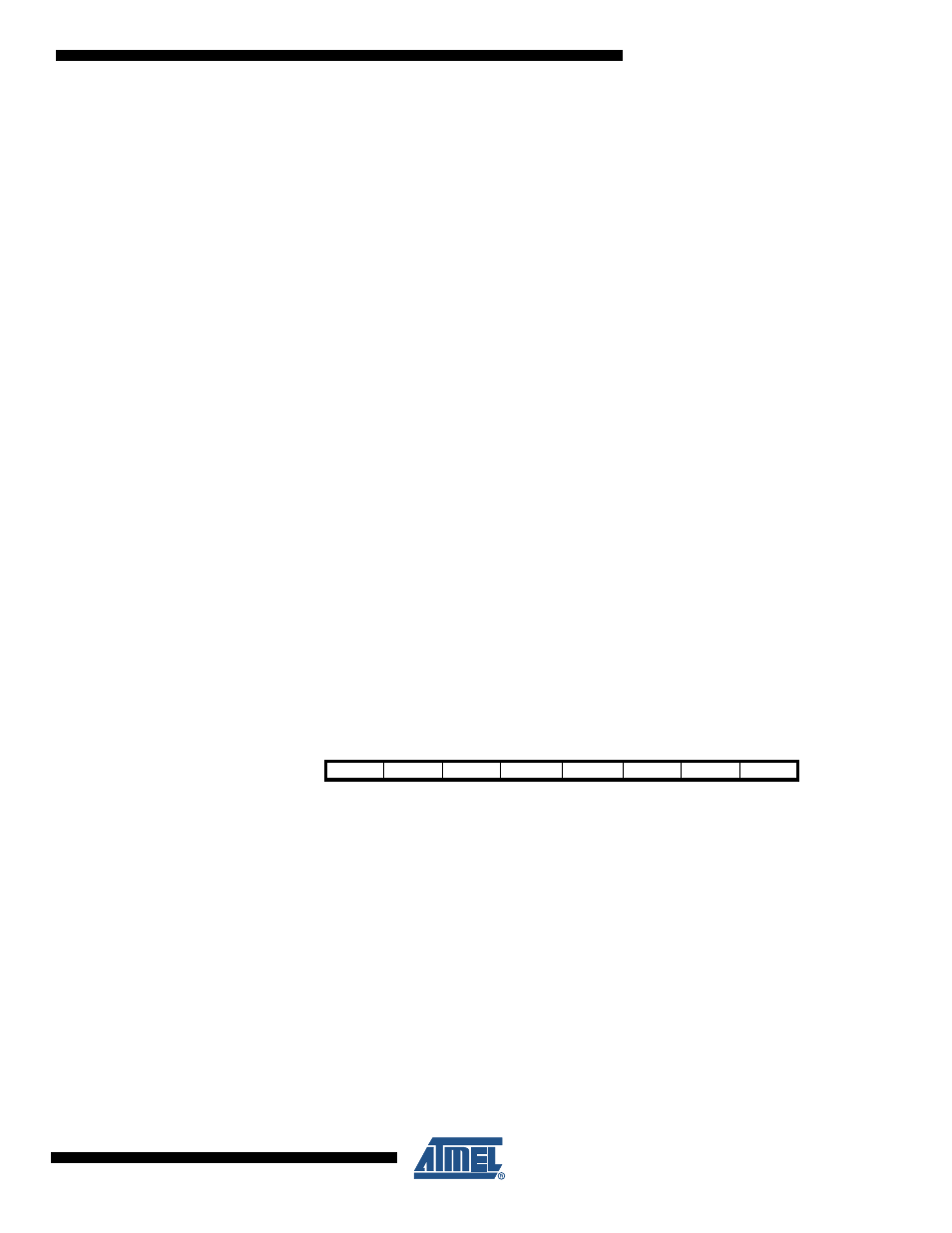

FCSR – FET Control and Status Register

• Bits 7:4 – Res: Reserved Bits

These bits are reserved bits in the ATmega4HVD/8HVD, and will always read as zero.

• Bit 3 – DUVRD: Deep Under-Voltage Recovery Disabled

When the DUVRD is cleared (zero), the FET Driver will be forced to operate in DUVR mode.

See

”DUVR – Deep Under-Voltage Recovery Mode operation” on page 117

for details. To

avoid that the FET driver tries to switch on the C-FET during current protection or during inter-

nal reset, the DUVRD bit is overridden to one by hardware in these cases. When this bit is set

(one), DUVR mode of the FET Driver will be disabled.

• Bit 2 – CPS: Current Protection Status

The CPS bit shows the status of the Current Protection. This bit is set (one) when a Current

Protection is active, and cleared (zero) otherwise.

Bit

7

6

5

4

3

2

1

0

–

–

–

–

DUVRD

CPS

DFE

CFE

FCSR

Read/Write

R

R

R

R

R/W

R

R/W

R/W

Initial Value

0

0

0

0

0

0

0

0