Receive side, Eceive – Rainbow Electronics DS26503 User Manual

Page 16

DS26503 T1/E1/J1 BITS Element

16 of 123

4.3 Receive Side

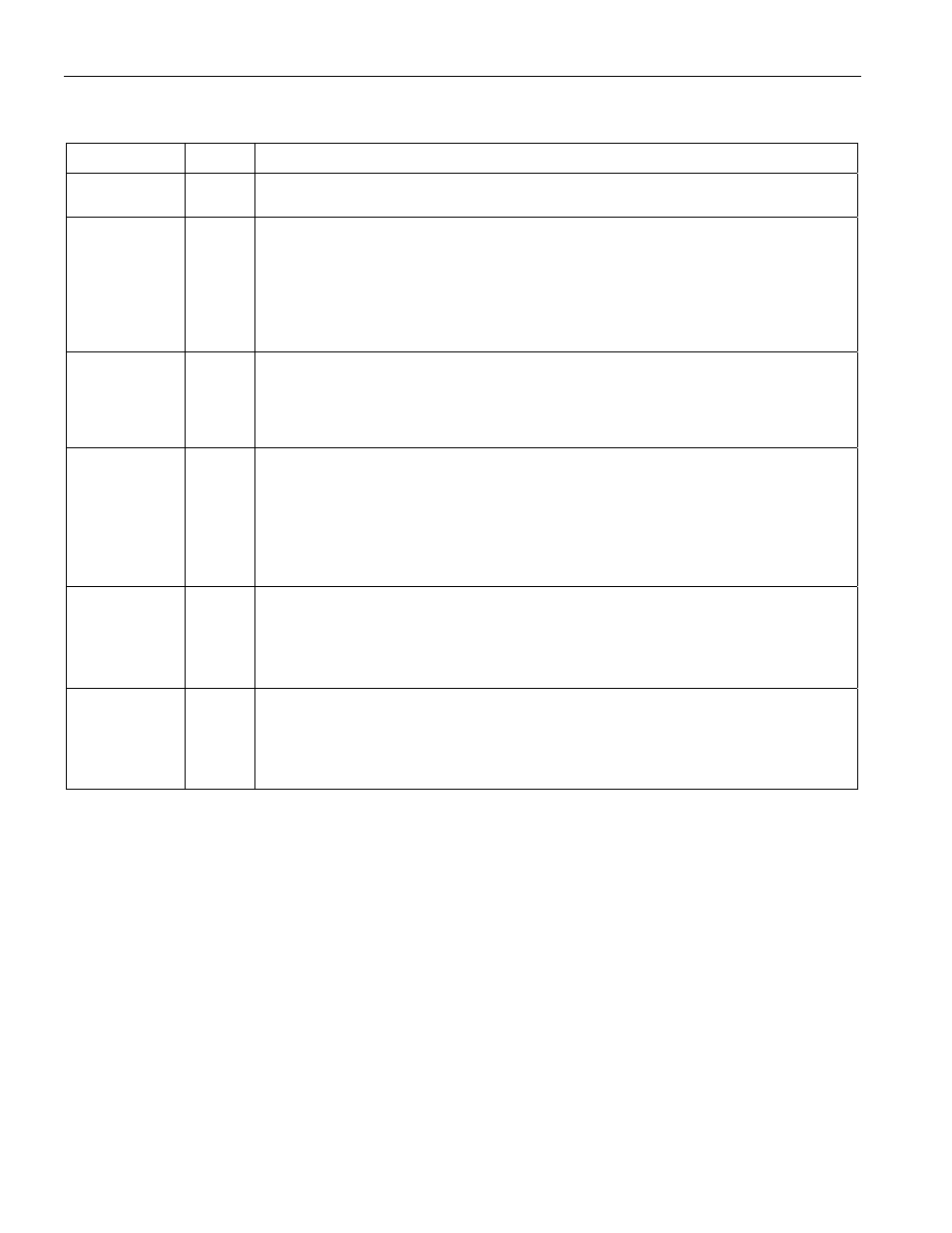

NAME TYPE

FUNCTION

RCLK O

Receive Clock. Recovered 1.544MHz (T1), 2.048MHz (E1), or 6312 kHz

(G.703 Synchronization Interface).

RS

O

Receive Sync

T1/E1 Mode: An extracted pulse, one RCLK wide, is output at this pin that

identifies either frame (IOCR1.5 = 0) or multiframe (IOCR1.5 = 1)

boundaries. If set to output frame boundaries, then through IOCR1.6, RS can

also be set to output double-wide pulses on signaling frames in T1 mode.

6312K Mode: This pin will be in a high-impedance state.

RSER O

Receive Serial Data

T1/E1 Mode: This is the received NRZ serial data updated on rising edges of

RCLK.

6312K Mode: This pin will be in a high-impedance state.

RLOF O

Receive Loss Of Frame. This output can be configured to be a Loss Of

Transmit Clock indicator via IOCR.4 when operating in T1 or E1 mode.

T1/E1 Mode: Set when the receive synchronizer is searching for frame

alignment (RLOF mode), or set when the signal at the TCLK pin has not

transitioned for approximately 15 periods of the scaled MCLK (LOTC mode).

6312K Mode: This pin will be in a high-impedance state.

RLOS O

Receive Loss Of Signal

T1 Mode: High when 192 consecutive zeros detected.

E1 Mode: High when 255 consecutive zeros detected.

6312K Mode: High when consecutive zeros detected for 65

ms typically.

RAIS O

Receive Alarm Indication Signal

T1 Mode: Will toggle high when receive Blue Alarm is detected.

E1 Mode: Will toggle high when receive AIS is detected.

6312K Mode: This pin will be in a high-impedance state.