Block diagrams, Igure 3-1. block diagram, Figure 3-1. block diagram – Rainbow Electronics DS26503 User Manual

Page 12: Rx liu rx liu t1/e1 ssm framer, Tx liu t1/e1 ssm formatter pll clock mux, Parallel/serial cpu i/f hardware controller, Jtag port

DS26503 T1/E1/J1 BITS Element

12 of 123

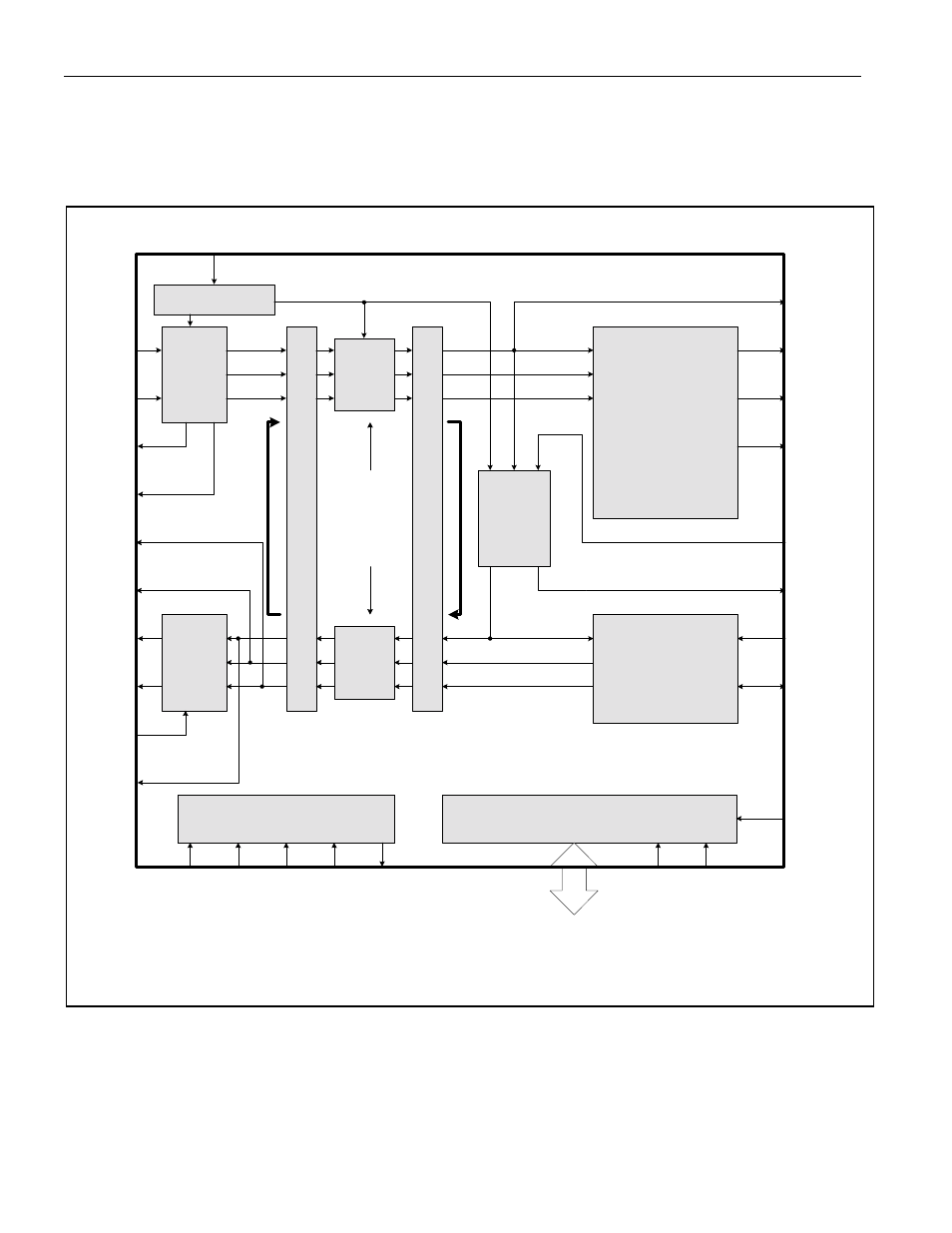

3. BLOCK DIAGRAMS

Figure 3-1. Block Diagram

RX

LIU

RX

LIU

T1/E1 SSM

FRAMER

CLOCK

- DATA

TX

LIU

T1/E1 SSM

FORMATTER

PLL

CLOCK

MUX

L

O

C

A

L

L

O

O

P

B

A

C

K

M

U

X

PARALLEL/SERIAL CPU I/F

HARDWARE CONTROLLER

RCLK

LOF_CCE

RSER

RS

PLL_OUT

TCLK

TSER

TS

+ DATA

RTIP

RRING

RLOS

RAIS

TTIP

JITTER

ATTENUATOR

CAN BE

ASSIGNED TO

RECEIVE OR

TRANSMIT PATH

OR DISABLED

MASTER CLOCK

MCLK

JTAG PORT

TSTRST

TX CLOCK

- DATA

+ DATA

JA

ENABLED

AND IN RX

PATH

JA

ENABLED

AND IN TX

PATH

DS26503

JTAG PORT

JTAG PORT

JTAG PORT

JTDO

JTDI

JTCLK

JTMS JTRST

BIS1

BIS0

JA

ENABLED

AND IN RX

PATH

R

E

M

O

T

E

L

O

O

P

B

A

C

K

M

U

X

PARALLEL,

SERIAL, OR

HARDWARE

CONTROLLER

JA CLOCK

See also other documents in the category Rainbow Electronics Communication:

- MAX12005 (14 pages)

- MAX7058 (14 pages)

- MAX9995 (13 pages)

- MAX7034 (13 pages)

- MAX7033 (16 pages)

- MAX9476 (8 pages)

- MAX9486 (8 pages)

- MAX14821 (29 pages)

- MAX9489 (11 pages)

- MAX9491 (11 pages)

- DS2130Q (22 pages)

- DS21458 (270 pages)

- DS3131 (174 pages)

- DS26502 (125 pages)

- DS2153Q (48 pages)

- DS2186 (11 pages)

- DS1842A (6 pages)

- DS3134 (203 pages)

- DS1876 (69 pages)

- DS1874 (88 pages)

- DS31256 (181 pages)

- DS2141A (35 pages)

- DS3184 (13 pages)

- DS2154 (69 pages)

- DS26504 (128 pages)

- DS3164 (12 pages)

- DS1852 (25 pages)

- DS2181A (32 pages)

- DS2151Q (46 pages)

- DS1843 (8 pages)

- DS2165Q (17 pages)

- DS3170 (233 pages)

- DS2180A (36 pages)

- DS2172 (20 pages)

- DS2152 (79 pages)

- DS1841 (16 pages)

- DS2182A (22 pages)

- DS2143Q (40 pages)

- DS2132A_Q (17 pages)

- DS1862 (42 pages)

- DS26519 (310 pages)

- DS2188 (11 pages)

- DS1875 (92 pages)

- DS33M33 (20 pages)