Table 2-20, Number, Table 2-21 – FUJITSU SPARC M4000 User Manual

Page 146: Psb, xsb, and

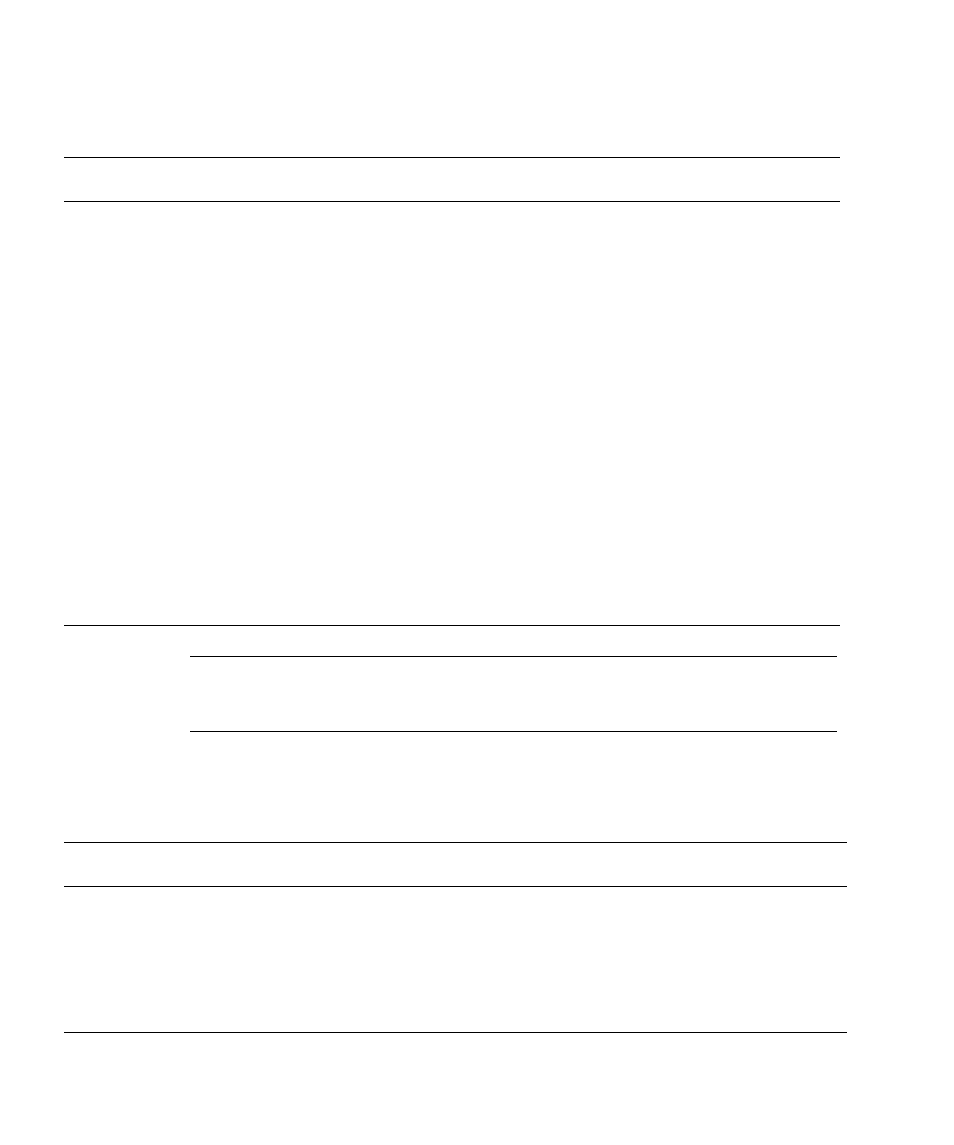

TABLE 2-20

Number of Domains and XSBs for Each System

System

Range of Domain

ID

Maximum Number of

XSBs

Memory Mirror (Note)

High-end system with

expansion cabinet

The system containing

up to 64 CPU chips.

(SPARC Enterprise

M9000)

0 - 23

64 (16 x 4)

Uni-XSBs only

Enabled

High-end systems

The system containing

up to 32 CPU chips.

(SPARC Enterprise

M9000)

0 - 23

32 (8 x 4)

The system containing

up to 16 CPU chips.

(SPARC Enterprise

M8000)

0 - 15

16 (4 x 4)

Midrange systems

The system containing

up to 8 CPU chips.

(SPARC Enterprise

M5000)

0 - 3

8 (2 x 4)

Enabled for both Uni-

XSBs and Quad-XSBs

The system containing

up to 4 CPU chips.

(SPARC Enterprise

M4000)

0 - 1

4 (1 x 4)

2-90

SPARC Enterprise Mx000 Servers XSCF User’s Guide • April 2008

Note –

Enabling Memory Mirror would require twice the amount of memory of a

domain used for operation. If the system board is a Quad-XSB in the high-end

systems, Memory Mirror cannot be used.

lists the PSB, XSB, and LSB numbers to be assigned.

TABLE 2-21

PSB, XSB, and LSB Numbers to be Assigned (Decimal)

PSB Number (Note)

XSB Number

(Uni-XSB) (Note)

XSB Number (Quad-XSB)

(Note)

LSB Number

00

00-0

00-0, 00-1, 00-2, 00-3

Independent values, 00 to 15, can

be arbitrarily specified in a

domain.

01

01-0

01-0, 01-1, 01-2, 01-3

02

02-0

02-0, 02-1, 02-2, 02-3

:

:

:

15

15-0

15-0, 15-1, 15-2, 15-3