1 reset, Reset, 20 btb entry 21 branch history – Intel NETWORK PROCESSOR IXP2800 User Manual

Page 95

Hardware Reference Manual

95

Intel

®

IXP2800 Network Processor

Intel XScale

®

Core

The BTB takes the current instruction address and checks to see if this address is a branch that was

previously seen. It uses bits [8:2] of the current address to read out the tag and then compares this

tag to bits [31:9,1] of the current instruction address. If the current instruction address matches the

tag in the cache and the history bits indicate that this branch is usually taken in the past, the BTB

uses the data (target address) as the next instruction address to send to the instruction cache.

Bit[1] of the instruction address is included in the tag comparison to support Thumb execution.

This organization means that two consecutive Thumb branch (B) instructions, with instruction

address bits[8:2] the same, will contend for the same BTB entry. Thumb also requires 31 bits for

the branch target address. In ARM* mode, bit[1] is 0.

The history bits represent four possible prediction states for a branch entry in the BTB.

shows these states along with the possible transitions. The initial state for branches stored in the

BTB is Weakly-Taken (WT). Every time a branch that exists in the BTB is executed, the history

bits are updated to reflect the latest outcome of the branch, either taken or not-taken.

The BTB does not have to be managed explicitly by software; it is disabled by default after reset

and is invalidated when the instruction cache is invalidated.

3.5.1.1

Reset

After Processor Reset, the BTB is disabled and all entries are invalidated.

Figure 20. BTB Entry

A9687-01

Branch Address[31:9,1]

TAG

Target Address[31:1]

History

Bits[1:0]

DATA

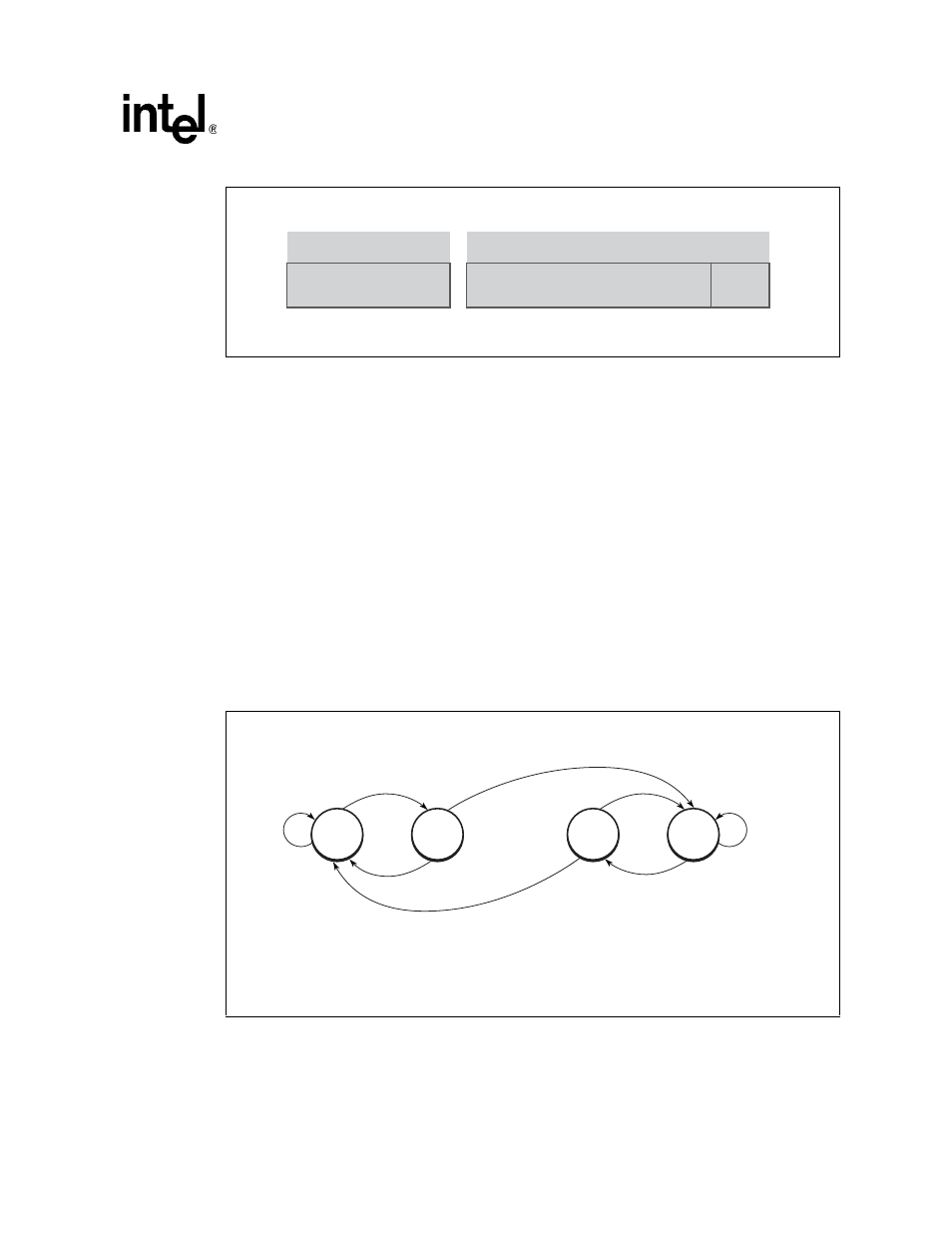

Figure 21. Branch History

A9688-01

SN

WN

WT

ST

N

o

tT

ak

en

Take

n

Taken

Not Taken

Not Taken

Taken

Not Ta

ken

Taken

Notes:

SN: Strongly Not Take

ST: Strongly Taken

WN: Weakly Not Taken

WT: Weakly Taken