Intel NETWORK PROCESSOR IXP2800 User Manual

Page 427

Hardware Reference Manual

427

Intel

®

IXP2800 Network Processor

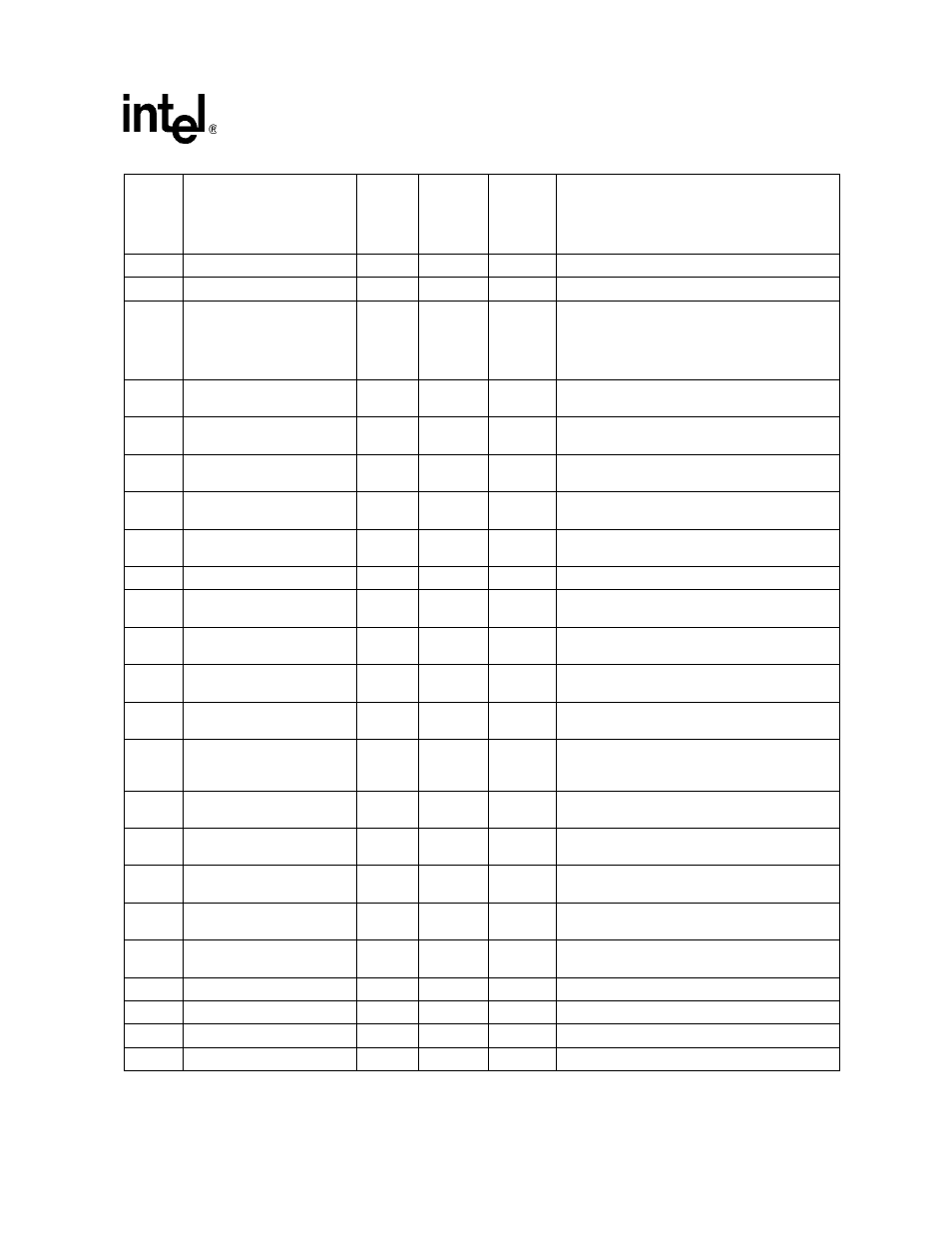

Performance Monitor Unit

33

DAP_DEQ_B3_DATA_RPH P_CLK

single

separate

Indicates pull data and command are being

dequeued from the data and command bank

FIFOs to the RMC (the command and data FIFOs

used in tandem for pulls to supply the address

and data respectively).

34

DAP_DEQ_B2_DATA_RPH P_CLK

single

separate

35

DAP_DEQ_B1_DATA_RPH P_CLK

single

separate

36

DAP_DEQ_B0_DATA_RPH P_CLK

single

separate

Indicates pull data and command are being

dequeued from the data and command bank

FIFOs to the RMC (the command and data FIFOs

used in tandem for pulls to supply the address

and data respectively).

37

csr_wr_data_avail P_CLK

single

separate

Indicates that CSR write data is ready to be

latched into the CSR.

38

bank3_enq_wph P_CLK

single

separate

Indicates pull data is being enqueued to a bank

FIFO in the pull bus interface block.

39

bank2_enq_wph P_CLK

single

separate

Indicates pull data is being enqueued to a bank

FIFO in the pull bus interface block.

40

bank1_enq_wph P_CLK

single

separate

Indicates pull data is being enqueued to a bank

FIFO in the pull bus interface block.

41

bank0_enq_wph P_CLK

single

separate

Indicates pull data is being enqueued to a bank

FIFO in the pull bus interface block.

42

reserved

43

DCB_BANK3_CMD_AVAL_

RDH

D_CLK

single

separate

Indicates that this bank FIFO has a command

available.

44

DCB_BANK2_CMD_AVAL_

RDH

D_CLK

single

separate

Indicates that this bank FIFO has a command

available.

45

DCB_BANK1_CMD_AVAL_

RDH

D_CLK

single

separate

Indicates that this bank FIFO has a command

available.

46

DCB_BANK0_CMD_AVAL_

RDH

D_CLK

single

separate

Indicates that this bank FIFO has a command

available.

47

DAP_CSR_READ_CMD_TA

KEN_WDH

D_CLK

single

separate

Indicates dequeueing of a CSR read command

and clears the CSR read request signal coming

out of d_command_bus_if.

48

DAP_BANK3_CMD_DEQ_

WDH

D_CLK

single

separate

Active to dequeue a DRAM command from bank

N's FIFO, generated by d_app block.

49

DAP_BANK2_CMD_DEQ_

WDH

D_CLK

single

separate

Active to dequeue a DRAM command from bank

N's FIFO, generated by d_app block.

50

DAP_BANK1_CMD_DEQ_

WDH

D_CLK

single

separate

Active to dequeue a DRAM command from bank

N's FIFO, generated by d_app block.

51

DAP_BANK0_CMD_DEQ_

WDH

D_CLK

single

separate

Active to dequeue a DRAM command from bank

N's FIFO, generated by d_app block.

52

split_cmd_wph P_CLK

single

separate

Active if the command will cross a 128-byte

boundary and thus be split across channels.

53

reserved

54

reserved

55

reserved

56

reserved

Table 184. IXP2800 Network Processor Dram CH2 PMU Event List (Sheet 3 of 5)