8 interrupt, 28 flow through the intel xscale – Intel NETWORK PROCESSOR IXP2800 User Manual

Page 132

132

Hardware Reference Manual

Intel

®

IXP2800 Network Processor

Intel XScale

®

Core

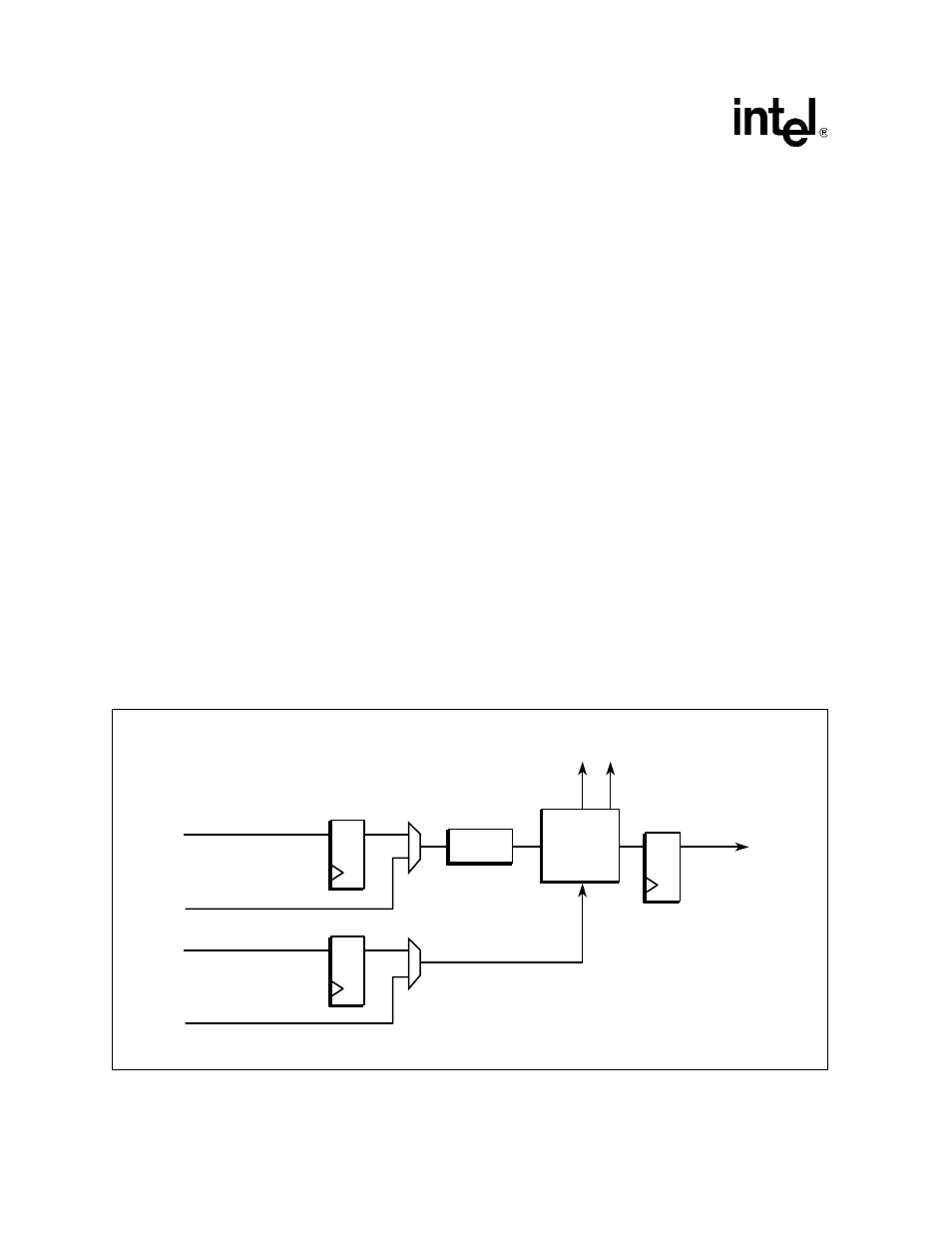

3.11.8

Interrupt

The Intel XScale

®

core CSR controller contains local CSR(s) and interrupts inputs from multiple

sources. The diagram in

shows the flow through the controller.

Within the Interrupt/CSR register block there are raw status registers, enable registers, and local

CSR(s). The raw status registers are the un-masked interrupt status. These interrupt status are

masked or steered to theIntel XScale

®

core’s IRQ or FIQ inputs by multiple levels of enable

registers.

•

{IRQ,FIQ}Status = (RawStatus & {IRQ,FIQ}Enable)

•

{IRQ,FIQ}ErrorStatus = (ErrorRawStatus & {IRQ,FIQ}ErrorEnable)

•

{IRQ,FIQ}ThreadStatus_$_# = ({IRQ,FIQ}ThreadRawStatus_$_# &

{IRQ,FIQ}ThreadEnable_$_#)

Each interrupt input is visible in the RawStatus register and is masked or steered by two level of

interrupt enable registers. The error and thread status are masked by one level of enable registers.

Their combination along with other interrupt sources contributes to the RawStatusReg. The

RawStatus is masked via IRQEnable/FIQEnable to trigger the IRQ and FIQ interrupt to the Intel

XScale

®

core.

The enable register’s bits are set and cleared through EnableSet and EnableClear registers. The

Status, RawStatus, and Enable registers are read-only, and EnableSet and EnableClear are

write-only. Also, Enable and EnableSet share the same address for reads and writes respectively.

Note that software needs to take into account the delay between the clearing of an interrupt

condition and having its status updated in the RawStatus registers. Also in the case of simultaneous

writes to the same registers, the value of the last write is recorded.

Figure 28. Flow Through the Intel XScale

®

Core Interrupt Controller

A9698-01

CAP_CSR_WR_ADDR

CAP_CSR_WR

From cbiAdr

From cbiData

cbrData

FIQ

IRQ

CAP_CSR_WR_DATA

CSR

Decode

Interrupt/

CSR

Registers