5 pci interrupt pin, Pci interrupt pin, 126 pci interrupts – Intel NETWORK PROCESSOR IXP2800 User Manual

Page 339: 125 irq interrupt options by stepping

Hardware Reference Manual

339

Intel

®

IXP2800 Network Processor

PCI Unit

9.3.5

PCI Interrupt Pin

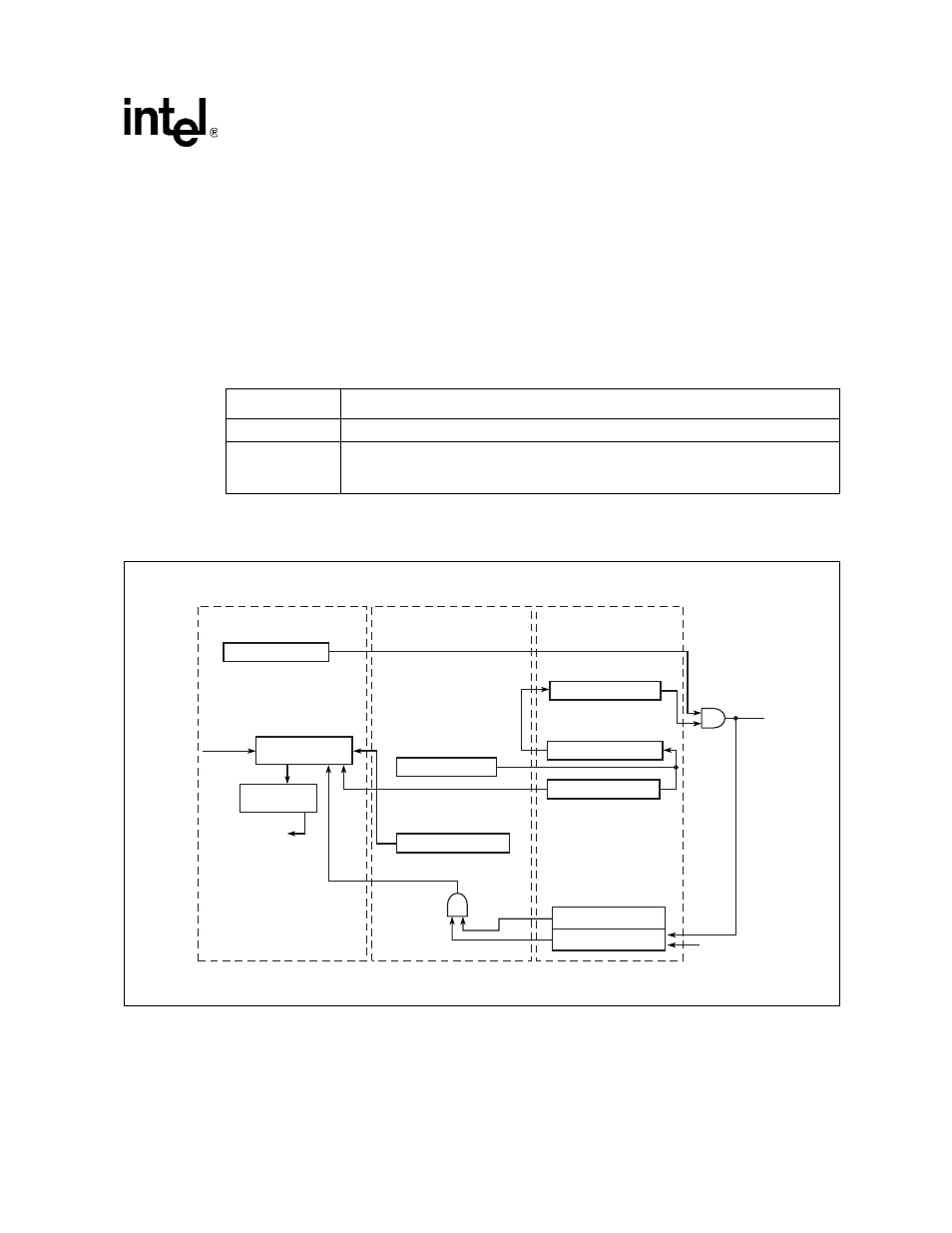

An external PCI interrupt can be generated in the following way:

•

The Intel XScale

®

core initiates a Doorbell interrupt XSCALE_INT_ENABLE.

•

One or more of the DMA channels have completed the DMA transfers.

•

The PNI bit is cleared by the Intel XScale

®

core to generate a PCI interrupt

•

An internal functional unit generates either an interrupt or an error directly to the PCI host.

describes how IRQ are generated for each silicon stepping.

shows how PCI interrupts are managed via the PCI and the Intel XScale

®

core.

Table 125. IRQ Interrupt Options by Stepping

Stepping

Description

A stepping

IRQ interrupts can be handled only by the Intel XScale

®

core.

B Stepping

IRQ interrupts can be handled by either the Intel XScale

®

core or a PCI host. Refer to the

description of the PCI_OUT_INT_MASK and PCI_OUT_INT_STATUS registers in the

Intel

®

IXP2400 and IXP2800 Network Processor Programmer’s Reference Manual.

Figure 126. PCI Interrupts

A9773-02

PCI_DOORBELL

XSCALE_DOORBELL

Enable PCI interrupt from

all doorbell bits

PCI_INTA#

PCI_INTB#

Bitwise

AND

{FIQ,IRQ}

RAW_INT_STATUS

{FIQ,IRQ}

_INT_ENABLE

PCI_OUT_INT_STATUS

DMA Channels (done)

PCI_OUT_INT_MASK

Tells whether or not PCI

interrupt was from Doorbell

XSCALE_INT_ENABLE

XSCALE_INT_STATUS

PCI_CONTROL

Other

interrupts

Intel XScale

®

Core interrupt

Registers

accessed

by Intel

®

XScale

®

Core

Intel XScale

®

Core writes

PNI bit to set PCI interrupt

Read Intel XScale

®

Core PCI interrupt to

determine interrupt

source

Intel XScale

®

Core sets

Doorbells bits to generate

an interrupt to the PCI

PCI sets Doorbells bits to

generate an interrupt to

the Intel XScale

®

Core