Intel, Ixp2800 network processor intel xscale, 154 hardware reference manual – Intel NETWORK PROCESSOR IXP2800 User Manual

Page 154

154

Hardware Reference Manual

Intel

®

IXP2800 Network Processor

Intel XScale

®

Core

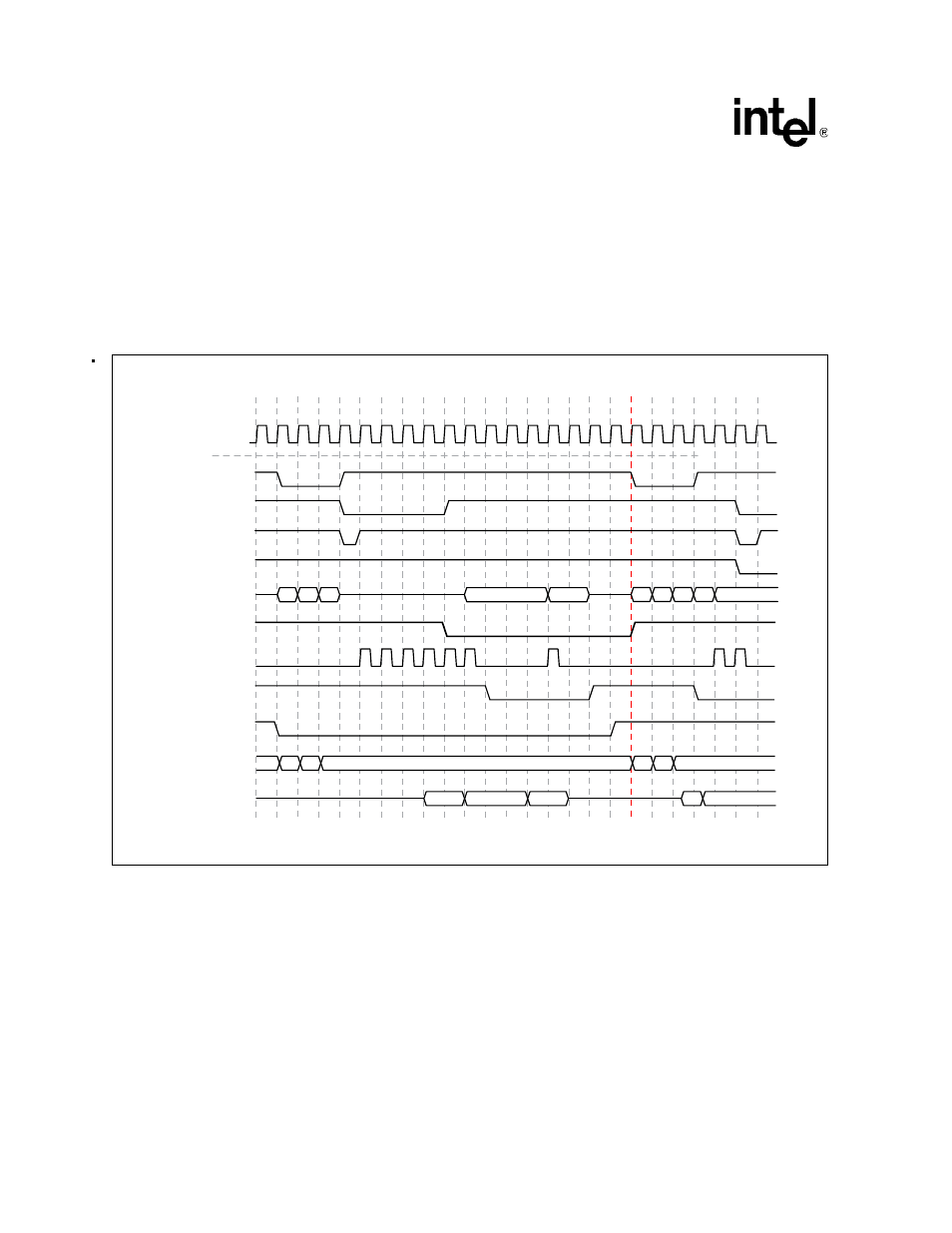

16-Bit Microprocessor Read Interface Protocol

, likewise depicts a single read transaction launched from the IXP2800 Network

Processor to the Lucent* TDAT042G5 device followed by a single read transaction. However, in

this case the read timing control register has to be programmed to setup=0, pulse width=7, and

hold =0.

In

, we can count twelve clock cycles used for the read transaction in total, (i.e., 240 ns)

for a clock cycle of 10 ns, excluding a turnaround cycle after that. It has the throughput of 7.7

Mbytes per second.

Figure 44. Mode 1 Single Read Transfer for Lucent* TDAT042G5 Device (B0)

B1746-04

SP_CLK

SP_ALE_L

SP_CS_L[1] /CS#

SP_WR_L/ADS#

SP_RD_L/R/W#

2

T0

T1

T2

T3 T4

T5

T6

T7

0

4

6

8

10

12

14

16

18

20

22

24

SP_AD[7:0]

SP_ACK_L /DT#

SP_CP

SP_OE_L

D[15:0]

A[23:0]

A[23:0]

SP_DIR

ADDR[15:0]

DATA[15:0]

A

[15:0]

A

[15:8]

A

[7:0]

A

[23:16]

A

[15:8]

A

[7:0]

A

[23:16]

D

[7:0]

D[15:8]

D[7:0]

D[7:0]

D[15:0]

2x[15:8]

D[7:0]

A

[15:0]

A

[7:0]

A

[7:0]

D[15:0]