2 absolute addressing mode, 3 indexed addressing mode, Absolute addressing mode – Intel NETWORK PROCESSOR IXP2800 User Manual

Page 42: Indexed addressing mode

42

Hardware Reference Manual

Intel

®

IXP2800 Network Processor

Technical Description

2.3.5.2

Absolute Addressing Mode

With Absolute addressing, any GPR can be read or written by any of the eight Contexts in a

Microengine. Absolute addressing enables register data to be shared among all of the Contexts,

e.g., for global variables or for parameter passing. All 256 GPRs can be read by Absolute address.

2.3.5.3

Indexed Addressing Mode

With Indexed addressing, any Transfer or Next Neighbor register can be read or written by any one

of the eight Contexts in a Microengine. Indexed addressing enables register data to be shared

among all of the Contexts. For indexed addressing the register number comes from the T_INDEX

register for Transfer registers or NN_PUT and NN_GET registers (for Next Neighbor registers).

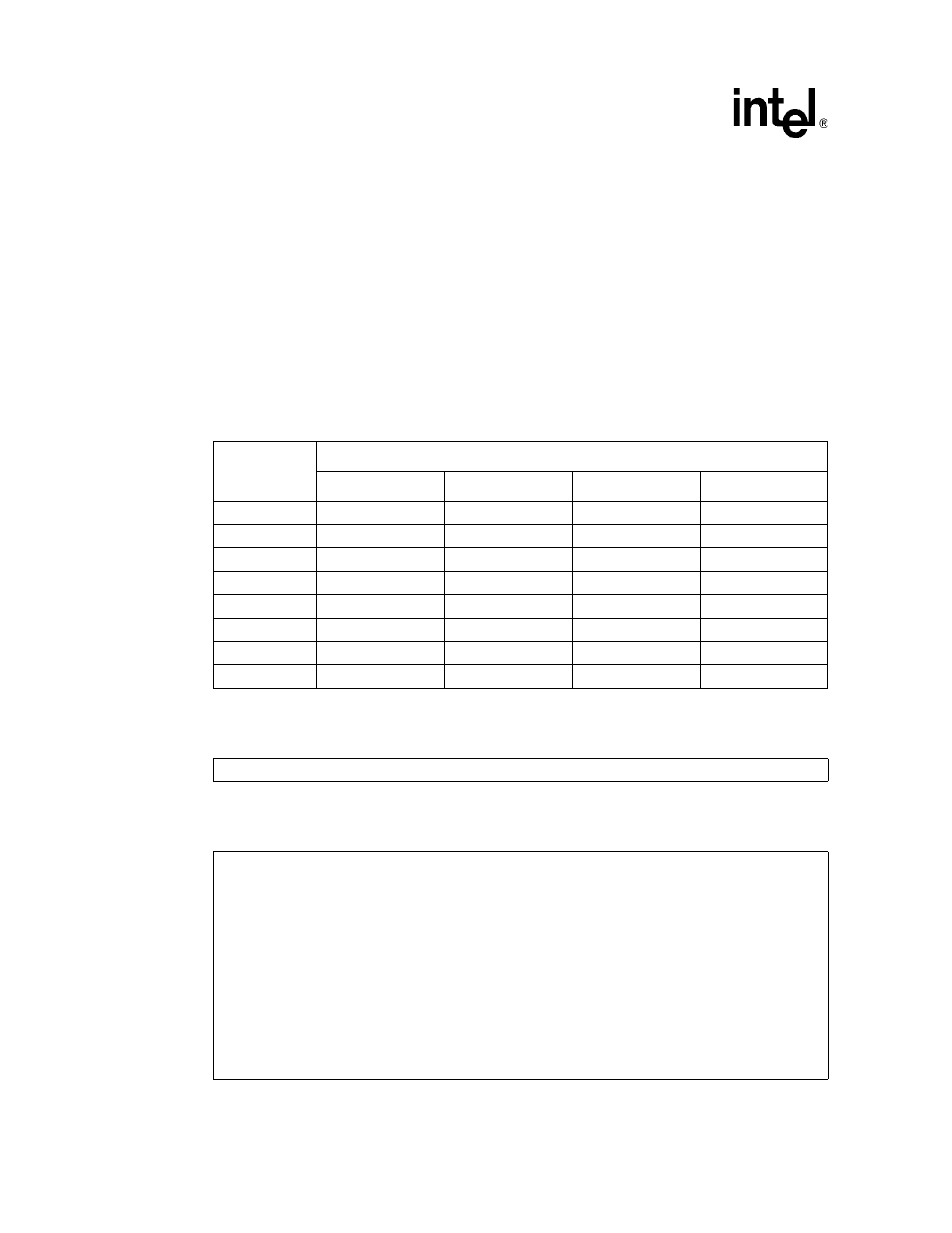

shows the Index Mode usage. Assume that the numbered bytes have been moved into

the S_TRANSFER_IN registers as shown.

If the software wants to access a specific byte that is known at compile-time, it will normally use

context-relative addressing. For example to access the word in transfer register 3:

If the location of the data is found at run-time, indexed mode can be used, e.g., if the start of an

encapsulated header depends on an outer header value (the outer header byte is in a fixed location).

Example 9. Use of Indexed Addressing Mode

Transfer

Register

Number

Data

31:24

23:16

15:8

7:0

0

0x00

0x01

0x02

0x03

1

0x04

0x05

0x06

0x07

2

0x08

0x09

0x0a

0x0b

3

0x0c

0x0d

0x0e

0x0f

4

0x10

0x11

0x12

0x013

5

0x14

0x15

0x16

0x17

6

0x18

0x19

0x1a

0x1b

7

0x1c

0x1d

0x1e

0x1f

alu[dest, --, B, $xfer3] ; move the data from s_transfer 3 to gpr dest

; Check byte 2 of transfer 0

; If value==5 header starts on byte 0x9, else byte 0x14

br=byte[$0, 2, 0x5, L1#], defer_[1]

local_csr_wr[t_index_byte_index, 0x09]

local_csr_wr[t_index_byte_index, 0x14]

nop ; wait for index registers to be loaded

L1#:

; Move bytes right justified into destination registers

nop ; wait for index registers to be loaded

nop ;

byte_align_be[dest1, *$index++]

byte_align_be[dest2, *$index++] ;etc.

; The t_index and byte_index registers are loaded by the same instruction.