1 spi-4, Spi-4, 89 full-duplex block diagram – Intel NETWORK PROCESSOR IXP2800 User Manual

Page 243: Figure 89, Is onl

Hardware Reference Manual

243

Intel

®

IXP2800 Network Processor

Media and Switch Fabric Interface

8.1.1

SPI-4

SPI-4 is an interface for packet and cell transfer between a physical layer (PHY) device and a link

layer device (the IXP2800 Network Processor), for aggregate bandwidths of OC-192 ATM and

Packet over SONET/SDH (POS), as well as 10 Gb/s Ethernet applications.

The Optical Internetworking Forum (OIF), www.oiforum.com, controls the SPI-4 Implementation

Agreement document.

SPI-4 has two types of transfers — Data when the RCTL signal is deasserted; Control when the

RCTL signal is asserted. The Control Word format is shown in

(this information is from

the SPI-4 specification, shown here for convenience).

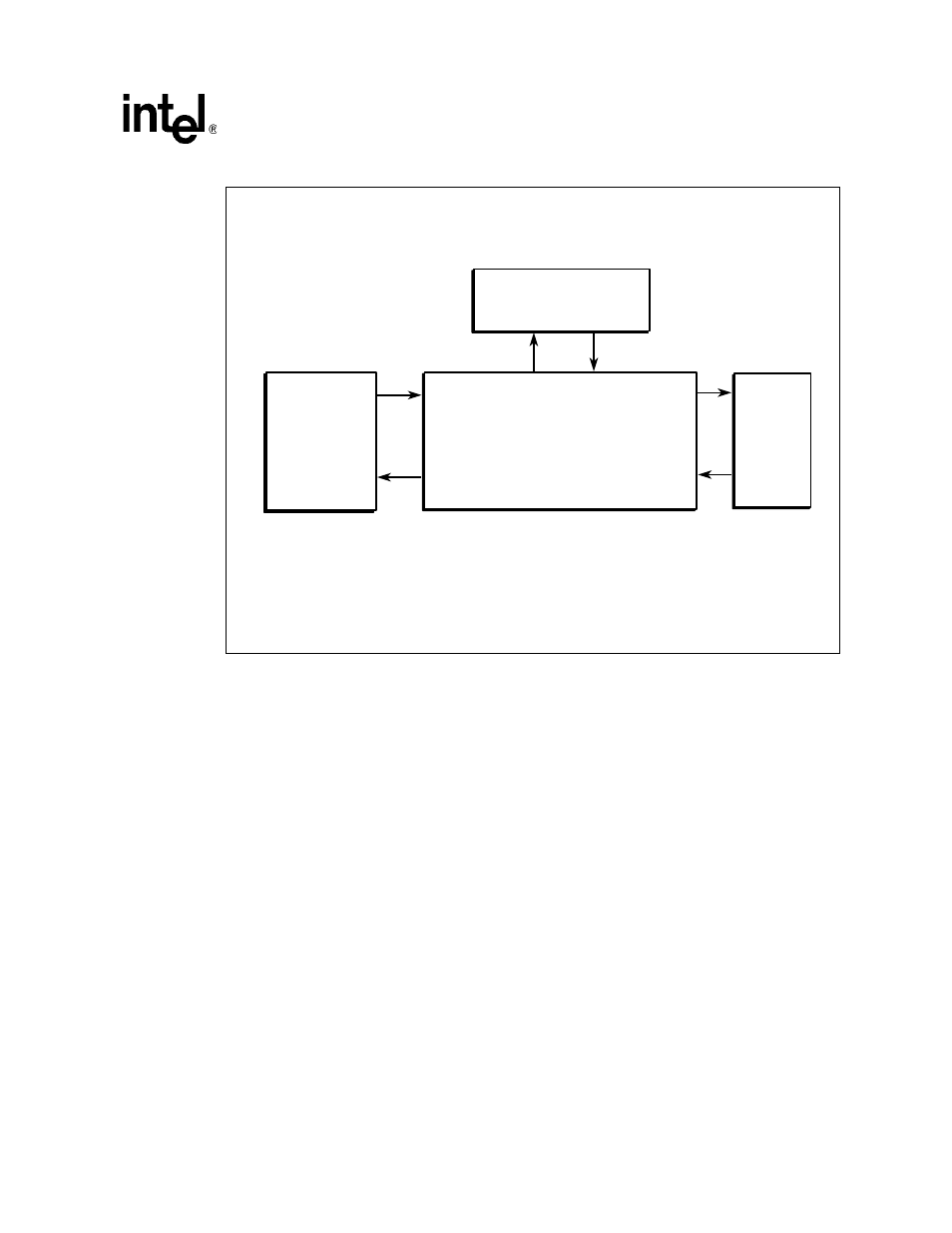

Figure 89. Full-Duplex Block Diagram

A9357-02

Intel

®

IXP2800

Network Processor

Framing/MAC

Device

(PHY)

UTOPIA-3

or IXBUS

Protocol

Receive and transmit protocol

is SPI-4 and CSIX on transfer-

by-transfer basis.

TDAT

RDAT

Bus Converter

Rx

Tx

Tx

Rx

Switch

Fabric

CSIX

Protocol

Notes:

The Bus Converter chip receives and transmits both SPI-4 and CSIX protocols from/to Intel

IXP2800 Network Processor. It steers the data, based on protocol, to either PHY device or

Switch Fabric. PHY interface can be UTOPIA-3, IXBUS, or any other required protocol.