Design block #(0011) – Intel NETWORK PROCESSOR IXP2800 User Manual

Page 429

Hardware Reference Manual

429

Intel

®

IXP2800 Network Processor

Performance Monitor Unit

11.4.6.31

IXP2800 Network Processor DRAM CH1 Events Target ID(010101) /

Design Block #(0011)

11.4.6.32

IXP2800 Network Processor DRAM CH0 Events Target ID(010110) /

Design Block #(0011)

80

bank2_enq_wph P_CLK

single

separate

Indicates this channel is enqueueing a DRAM

command for bank2.

81

bank1_enq_wph P_CLK

single

separate

Indicates this channel is enqueueing a DRAM

command for bank1.

82

bank0_enq_wph P_CLK

single

separate

Indicates this channel is enqueueing a DRAM

command for bank0.

83

push2split_cmd_fifo_wph P_CLK

single

separate

Indicates this channel is enqueueing a DRAM

command which is split between two channels.

84

push2inlet_fifo_wph P_CLK

single

separate

Indicates this channel is enqueueing a DRAM

command which fits entirely in this channel.

85

valid_dram_cmd_wph P_CLK

single

separate

Indicates the command bus' target ID is DRAM.

86-127

reserved

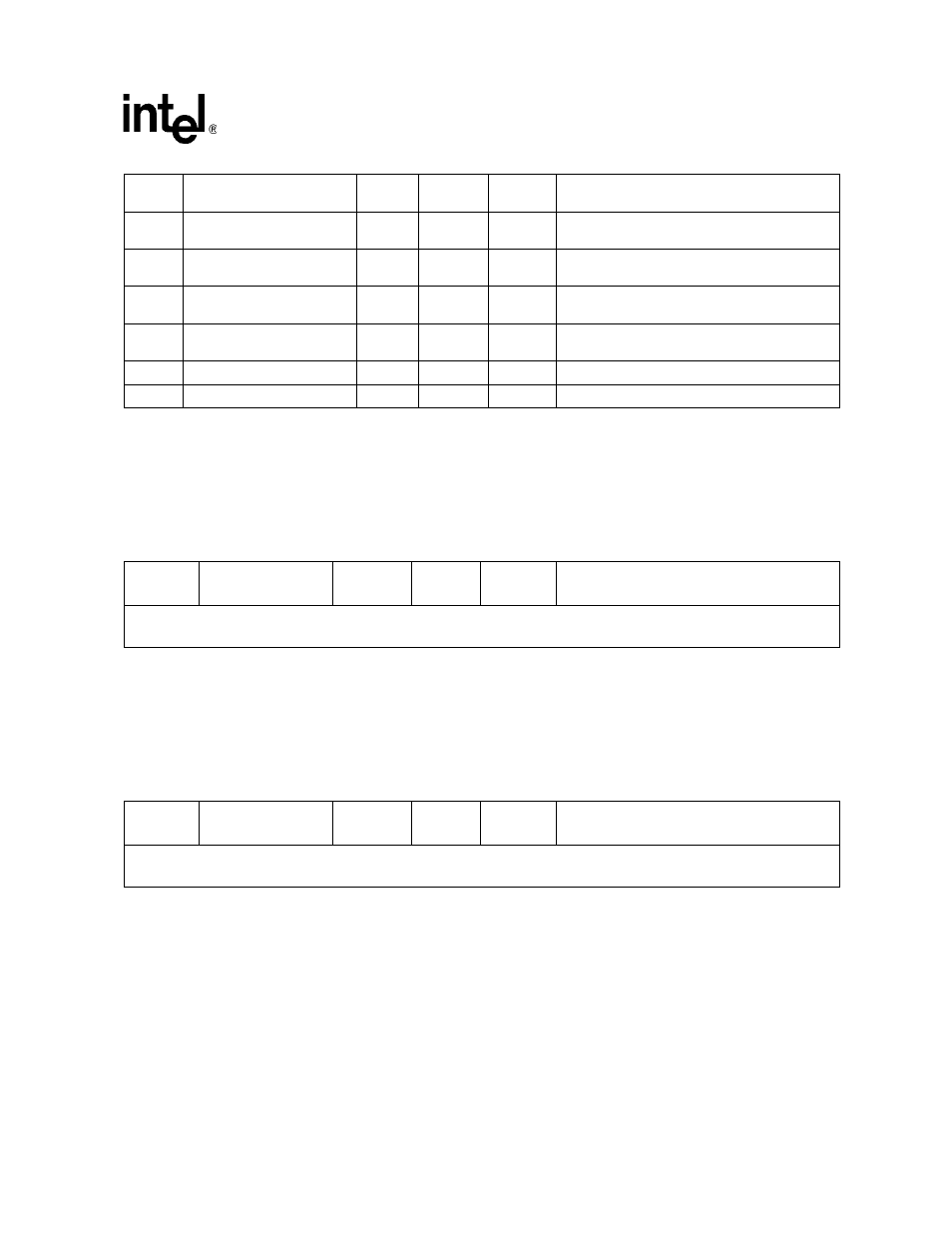

Table 184. IXP2800 Network Processor Dram CH2 PMU Event List (Sheet 5 of 5)

Table 185. IXP2800 Network Processor Dram CH1 PMU Event List

Event

Number

Event Name

Clock

Domain

Pulse/

Level

Burst

Description

Note:

1. All the Dram Channels have same event lists. Please reference Channel 2 Event lists.

Table 186. IXP2800 Network Processor Dram CH0 PMU Event List

Event

Number

Event Name

Clock

Domain

Pulse/

Level

Burst

Description

Note:

1. All the Dram Channels have same event lists. Please reference Channel 2 Event lists