73 queue format – Intel NETWORK PROCESSOR IXP2800 User Manual

Page 215

Hardware Reference Manual

215

Intel

®

IXP2800 Network Processor

SRAM Interface

There are two different modes for the dequeue command. One mode removes an entire buffer from

the queue. The second mode removes a piece of the buffer (referred to as a cell). The mode (cell

dequeue or buffer dequeue) is selectable on a buffer-by-buffer basis by setting the

cell_count

bits (

<

30

:

24

>

) in the link longword.

A ring is an ordered list of data words stored in a fixed block of contiguous addresses. A ring is

described by a head pointer and a tail pointer. Data is written, using the

put

command, to a ring at

the address contained in the tail pointer and the tail pointer is incremented. Data is read, using the

get

command, from a ring at the address contained in the head pointer and the head pointer is

incremented. Whenever either pointer reaches the end of the ring, the pointer is wrapped back to

the address of the start of the ring.

A journal is similar to a ring. It is generally used for debugging. Journal commands only write to

the data structure. New data overwrites the oldest data. Microcode can choose to tag the journal

data with the Microengine number and CTX number of the journal writer.

The

Q_array

to support queuing, rings and journals contains 64 registers per SRAM channel. For

a design with a large number of queues, the queue descriptors cannot all be stored on the chip, and

thus a subset of the queue descriptors (16) is cached in the Q_array. (To implement the cache, 16

contiguous Q_array registers must be allocated.) The cache tag (the mapping of queue number to

Q_array

registers) for the

Q_array

is maintained by microcode in the CAM of a Microengine.

The writeback and load of the cached registers in the

Q_array

is under the control of that

microcode.

Note: The size of the

Q_array

does not set a limit on the number of queues supported.

For other queues (free buffer pools, for example), rings, and journals, the information does not

need to be subsetted and thus can be loaded into the

Q_array

at initialization time and left there to

be updated solely by the SRAM controller.

The sum total of the cached queue descriptors plus the number of rings, journals, and static queues

must be less than or equal to 64 for a given SRAM channel.

The fields and sizes of the

Q_array

registers are shown in

. All addresses

are of type longword, and are 32 bits in length.

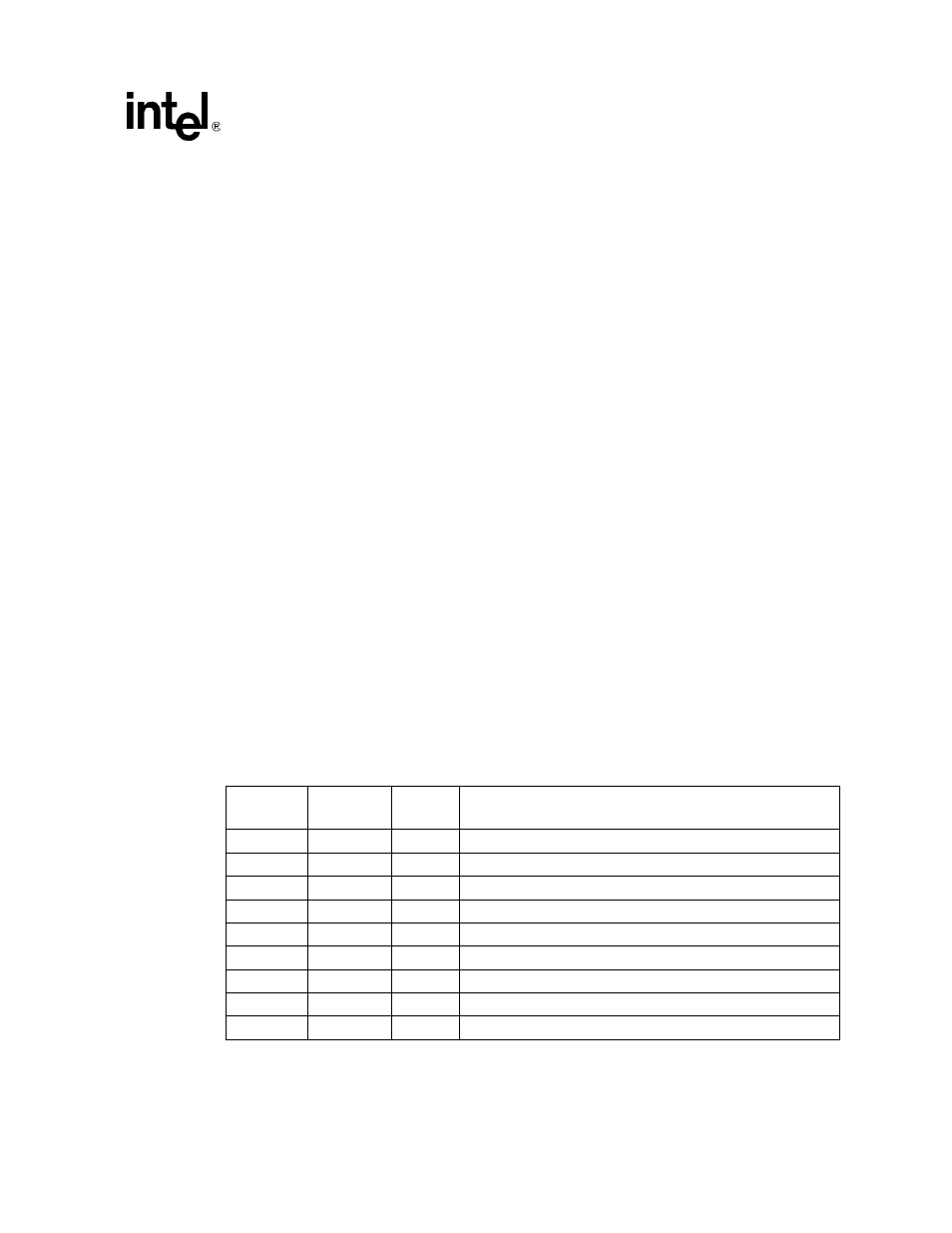

Table 73. Queue Format

Name

Longword

Number

Bit

Number

1

1.

Bits

31

:

24

of longword number 2 are available for use by microcode.

Definition

EOP

0

31

End of Packet — decrement Q_count on dequeue

SOP

0

30

Start of Packet — used by the programmer

Cell Count

0

29:24

Number of cells in the buffer

Head

0

23:0

Head pointer

Tail

1

23:0

Tail pointer

Q_count

2

23:0

Number of packets on the queue or number of buffers on the queue

SW_Private

2

31:24

Ignored by hardware, returned to Microengine

Head Valid

N/A

Cached head pointer valid — maintained by hardware

Tail Valid

N/A

Cached tail pointer valid — maintained by hardware