12 dram pull arbiter description, 72 dram push arbiter functional blocks, 69 dpla description – Intel NETWORK PROCESSOR IXP2800 User Manual

Page 204: Figure 72

204

Hardware Reference Manual

Intel

®

IXP2800 Network Processor

DRAM

The DRM Push Arbiter boundary conditions are:

•

Make sure each of the push_request queues assert the full signal and back pressure the

requesting unit.

•

Maintain 100% bus utilization, i.e., no holes.

5.12

DRAM Pull Arbiter Description

The general data flow for a push operation is as shown in

. The DRAM Pull Arbiter

functional blocks are shown in

The pull arbiter is very similar to the push arbiter, except that it gathers the data from a data source

ID and delivers it to the requesting unit where it is written to DRAM memory.

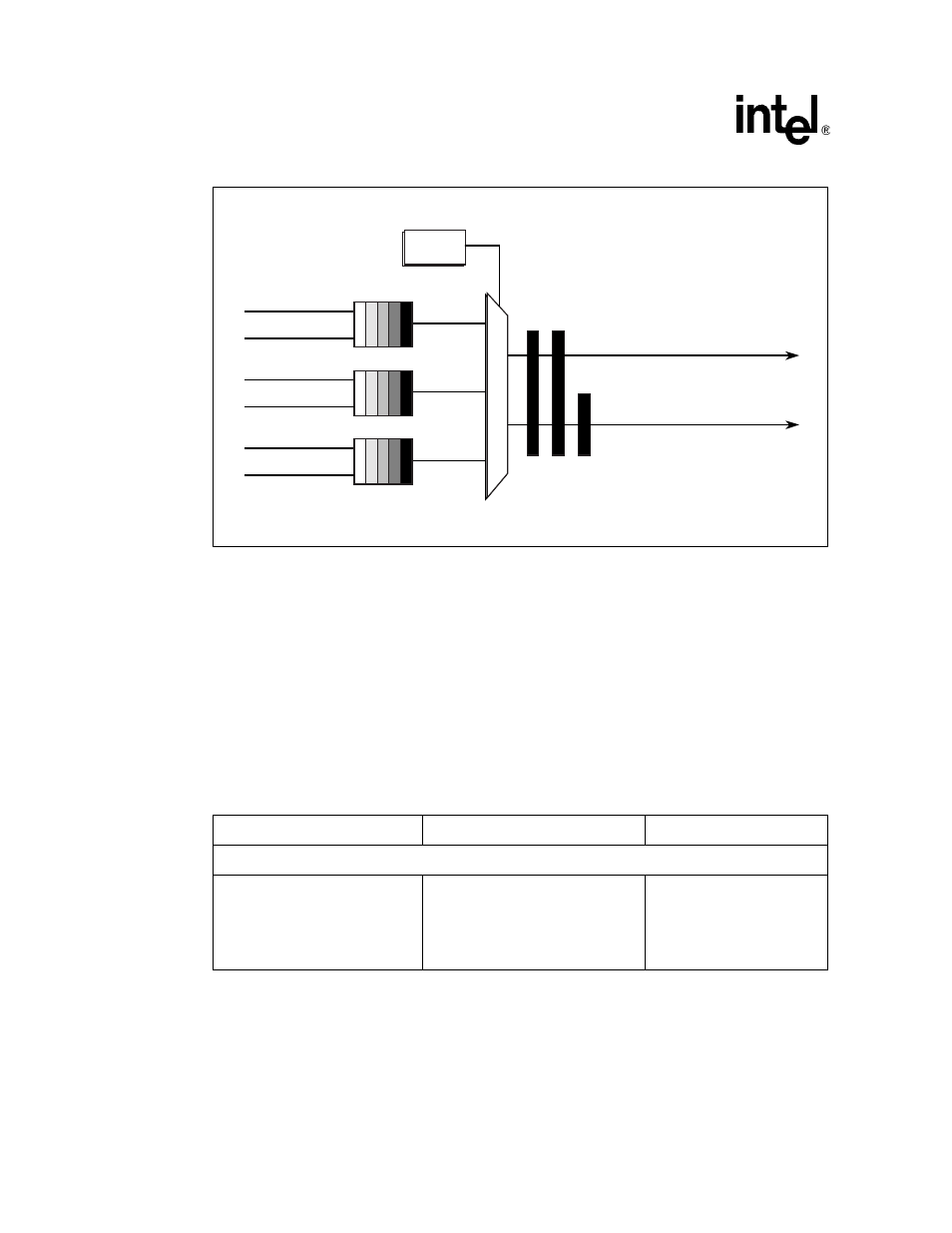

Figure 72. DRAM Push Arbiter Functional Blocks

A9732-01

D0_PUSH_REQ

DPXX_PUSH_ID

Round

Robin

A

R

B

I

T

E

R

D0_PUSH_ID

D1_PUSH_REQ

D1_PUSH_ID

D2_PUSH_REQ

D2_PUSH_ID

D0_PUSH_DATA

D1_PUSH_DATA

D2_PUSH_DATA

DPXX_PUSH_DATA

Table 69. DPLA Description

Pull Bus Master/Requestor

Data Source

Data Destination

IXP2800 Network Processor

D0 Unit

D1 Unit

D2 Unit

TC0 Cluster (Microengine 0 – 7)

TC1 Cluster (Microengine 8 – 15)

Intel XScale

®

core

PCI Unit

MSF Unit

Current Master