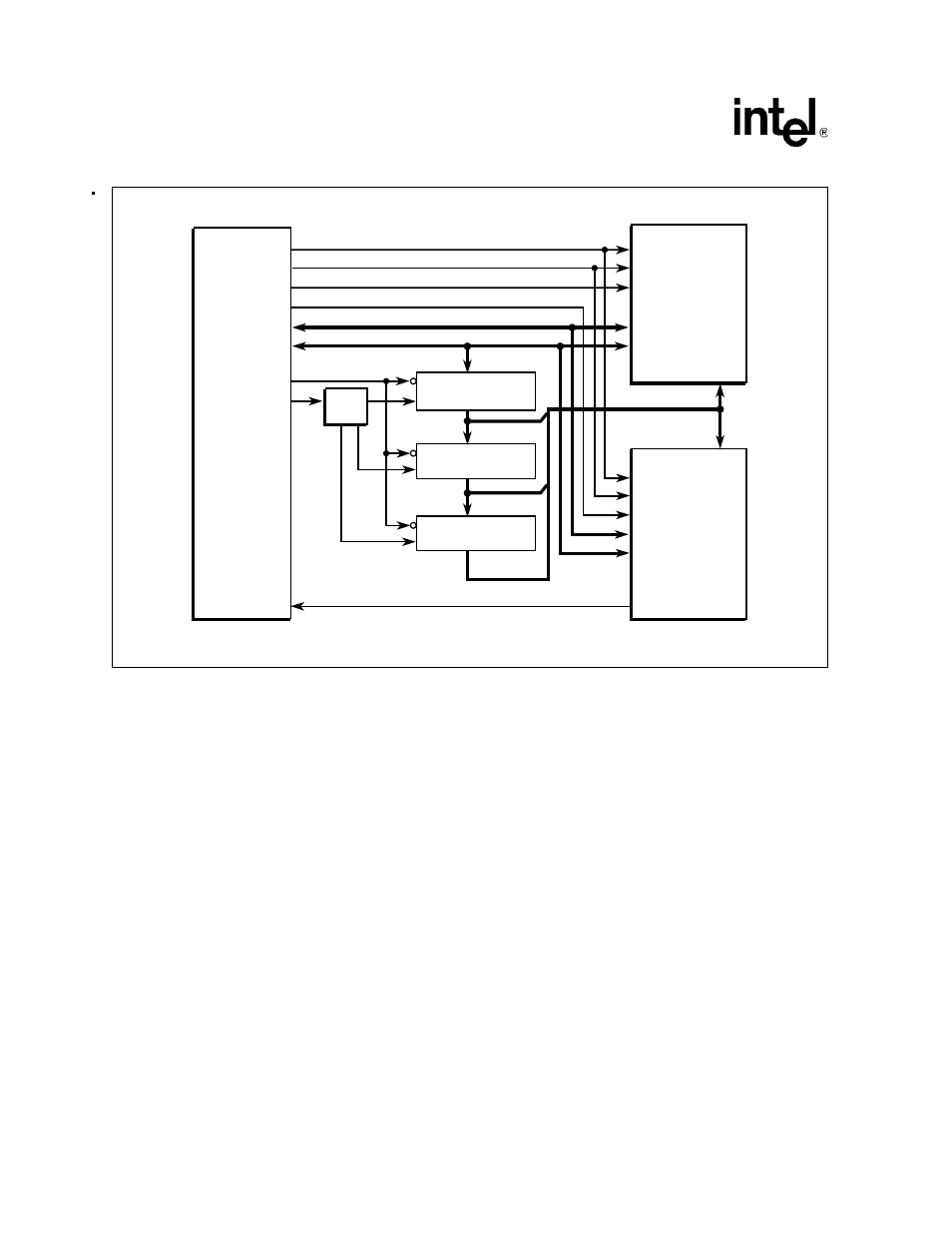

6 slowport 8-bit device bus protocols, 37 slowport example application topology, Figure 37 – Intel NETWORK PROCESSOR IXP2800 User Manual

Page 146: Demonstrates, Shown in

146

Hardware Reference Manual

Intel

®

IXP2800 Network Processor

Intel XScale

®

Core

3.12.7.6

Slowport 8-Bit Device Bus Protocols

The write/read transfer protocols are discussed in the following sections. The burst transfers are

going to be broken down into single mode transfer. For each single write/read transaction, it can be

either fixed-timed transaction or self-timing transaction. The fixed-timed transaction has the

response fixed in a certain period, that can be controlled by the timing control registers.

For the self-timing transaction, the response timing is dictated by the peripheral device. Hence,

wait states can be inserted during the transaction. All the back-to-back transactions are intervened

with one clock cycle. The Slowport clock, SP_CLK, shown in the following waveform diagrams,

is generated by dividing the PLPL_APB_CLK. The divisor used is specified in the clock control

register, SP_CCR.

Figure 37. Slowport Example Application Topology

A9318-02

SP_RD_L

SP_CS_L[0]

SP_CS_L[1]

SP_A[1:0]

CE#

CP

D[7:0]

Q[7:0]

74f377

SP_WR_L

OE_L

A[1:0]

CS_L

WE_L

D[7:0]

A[24:2]

A[1:0]

CS_L

WE_L

D[7:0]

ACK_L

A[24:2]

Intel

®

IXP2800

Network

Processor

SP_AD[7:0]

SP_ALE_L

SP_CLK

SP_ACK_L

CE#

CP

D[7:0]

A[24:18]

A[17:10]

A[9:2]

Q[7:0]

74f377

CE#

CP

D[7:0]

Q[7:0]

74f377

OE_L

Clock

Driver

CY2305