3 queue data structure commands, Queue data structure commands – Intel NETWORK PROCESSOR IXP2800 User Manual

Page 213

Hardware Reference Manual

213

Intel

®

IXP2800 Network Processor

SRAM Interface

6.4.3

Queue Data Structure Commands

The ability to enqueue and dequeue data buffers at a fast rate is key to meeting chip performance

goals. This is a difficult problem as it involves dependent memory references that must be turned

around very quickly. The SRAM controller includes a data structure (called the Q_array) and

associated control logic to perform efficient enqueue and dequeue operations. Optionally, this

hardware (or a portion of it) can be used to implement rings and journals.

A queue is an ordered list of data buffers stored at non-contiguous addresses. The first buffer added

to the queue will be the first buffer removed from the queue. Queue entries are joined together by

creating links from one data buffer to the next. This hardware implementation supports only a

forward link. A queue is described by a pointer to its first entry (called the head) and a pointer to its

last entry (the tail). In addition, there is a count of the number of items currently on the queue. This

triplet (head, tail, and count) is referred to as the queue descriptor. In the IXP2800 chips, the queue

descriptor is stored in that order — head first, then tail, then count. The longword alignment of the

head addresses for all queue descriptors must be a power of two. For example, when there are no

extra parameters on the queue descriptor, there will be one unused longword per queue descriptor.

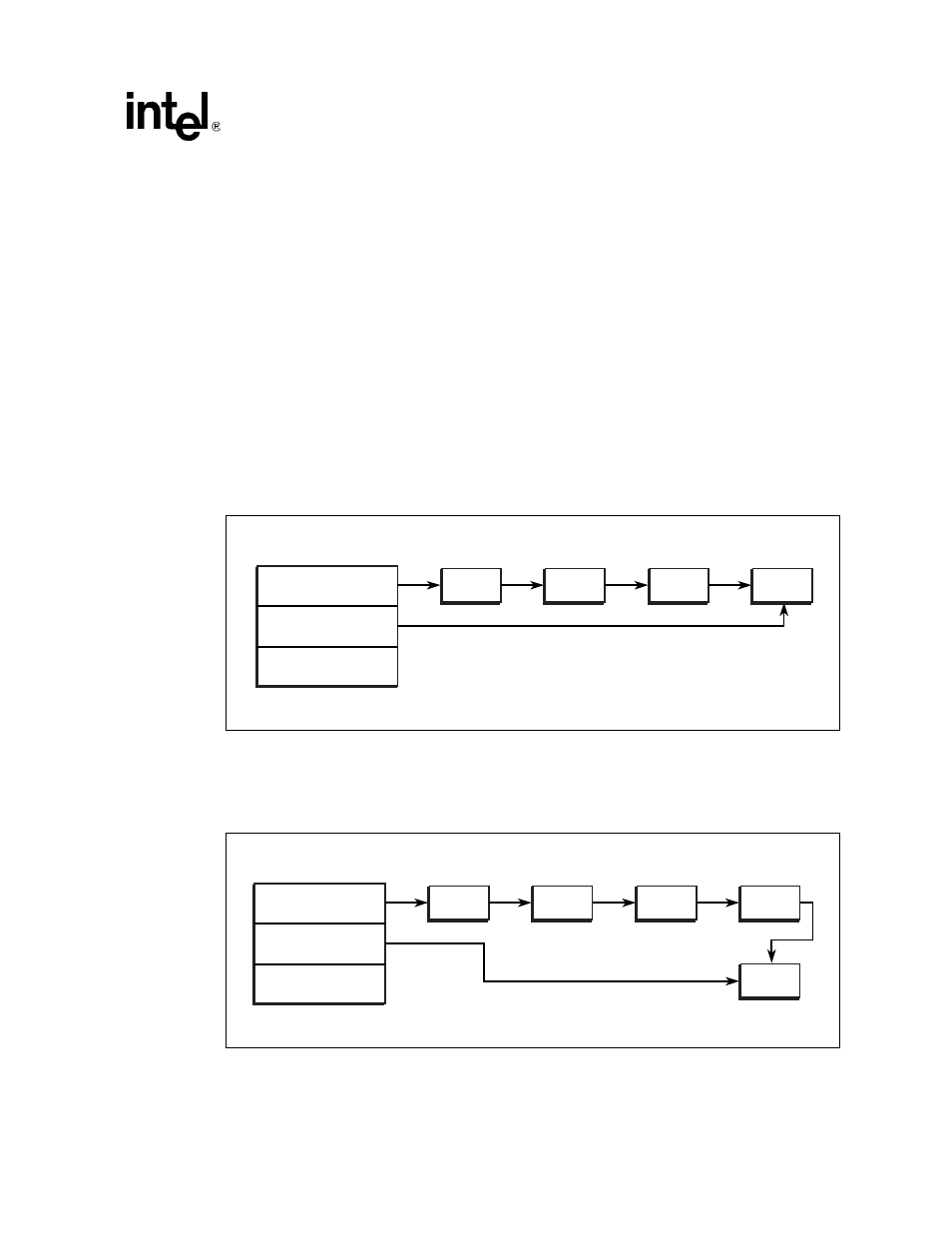

shows a queue descriptor and queue links for a queue containing four entries.

There are two different versions of the enqueue command,

ENQ_tail_and_link

and

ENQ_tail

.

ENQ_tail_and_link

enqueues one buffer at a time. In

, issuing an

ENQ_tail_and_link

to buffer link address

Z

results in the queue shown in

.

Figure 77. Queue Descriptor with Four Links

A9736-01

Head: A

Tail: D

Q_Count: 4

B

A:

C

B:

D

C:

No Link

D:

Figure 78. Enqueueing One Buffer at a Time

A9737-01

Head: A

Tail: Z

Q_Count: 5

B

A:

C

B:

D

C:

Z

D:

No Link

Z: