Endian with swap), Without swap), Table 137 – Intel NETWORK PROCESSOR IXP2800 User Manual

Page 354: Intel, 354 hardware reference manual

354

Hardware Reference Manual

Intel

®

IXP2800 Network Processor

PCI Unit

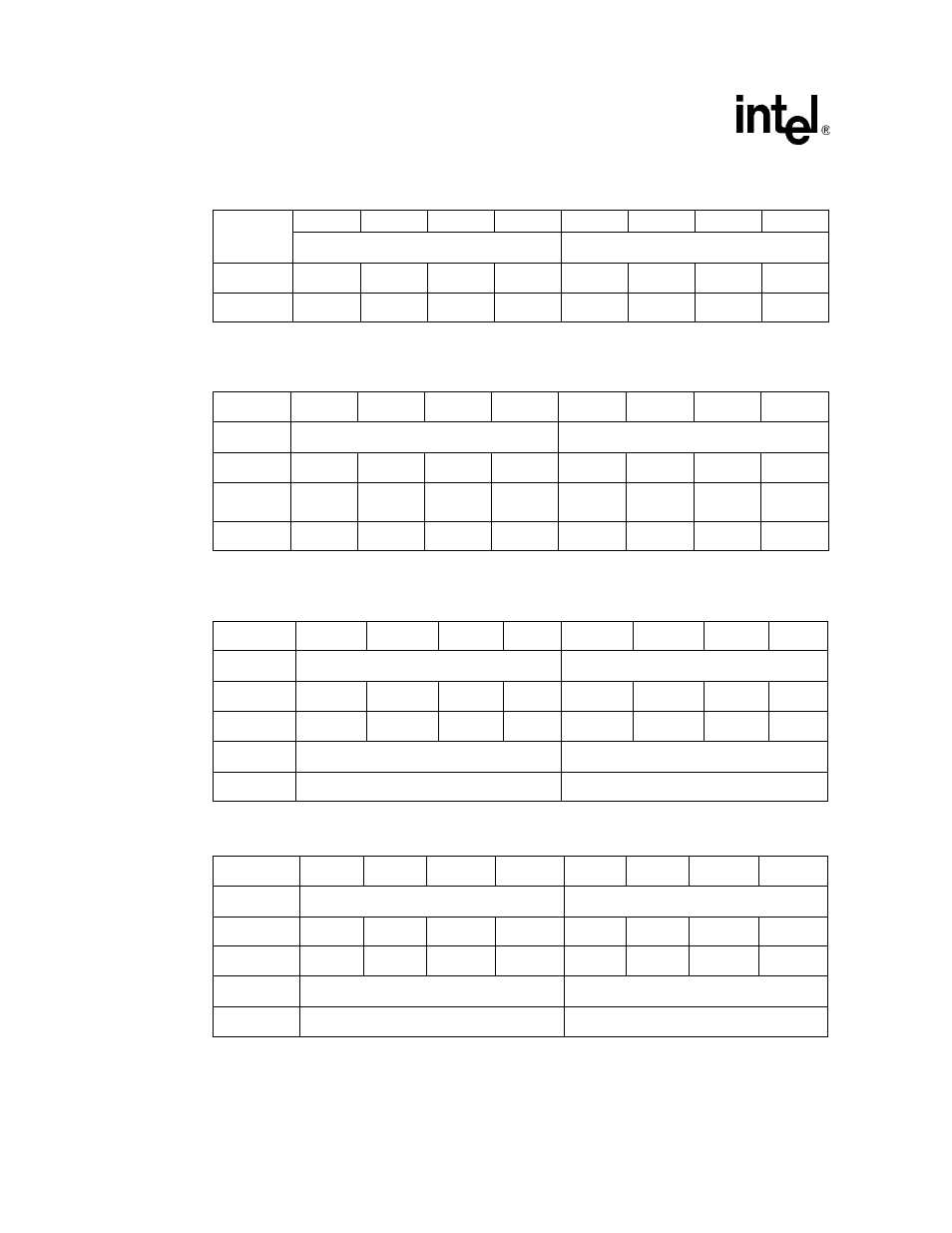

Table 134. Byte Lane Alignment for 64-Bit PCI Data Out (Big-Endian to 64 Bits PCI Little

Endian with Swap)

SRAM Data

IN[7:0]

IN[15:8]

IN[23:16]

IN[31:24]

IN[7:0]

IN[15:8]

IN[23:16]

IN[31:24]

Longword1 (32 bits)

LW1 drive after LW0

Longword0 ((32 bits)

LW0 drive first

DRAM Data

IN[39:32]

IN[47:40]

IN[55:48]

IN[63:56]

IN[7:0]

IN[15:8]

IN[23:16]

IN[31:24]

PCI Side

OUT[63:56] OUT[55:48] OUT[47:40] OUT[39:32] OUT[31:24] OUT[23:16]

OUT[15:8]

OUT[7:0]

Table 135. Byte Lane Alignment for 64-Bit PCI Data Out (Big-Endian to 64 Bits PCI Big-Endian

without Swap)

SRAM Data

IN[7:0]

IN[15:8]

IN[23:16]

IN[31:24]

IN[7:0]

IN[15:8]

IN[23:16]

IN[31:24]

Longword1 (32 bits)

LW1 drive after LW0

Longword0 ((32 bits)

LW0 drive first

DRAM Data

IN[39:32]

IN[47:40]

IN[55:48]

IN[63:56]

IN[7:0]

IN[15:8]

IN[23:16]

IN[31:24]

direct map

pci to dram

IN[7:0]

IN[15:8]

IN[23:16]

IN[31:24]

IN[7:0]

IN[15:8]

IN[23:16]

IN[31:24]

PCI Side

OUT[39:32] OUT[47:40] OUT[55:48] OUT[63:56]

OUT[7:0]

OUT[15:8]

OUT[23:16] OUT[31:24]

Table 136. Byte Lane Alignment for 32-Bit PCI Data Out (Big-Endian to 32 Bits PCI Little

Endian with Swap)

SRAM Data

IN[7:0]

IN[15:8]

IN[23:16]

IN[31:24]

IN[7:0]

IN[15:8]

IN[23:16]

IN[31:24]

Longword1 (32 bits)

LW1 drive after LW0

Longword0 ((32 bits)

LW0 drive first

DRAM Data

IN[39:32]

IN[47:40]

IN[55:48]

IN[63:56]

IN[7:0]

IN[15:8]

IN[23:16]

IN[31:24]

PCI Data

OUT[31:24]

OUT[23:16]

OUT[15:8]

OUT[7:0]

OUT[31:24]

OUT[23:16]

OUT[15:8]

OUT[7:0]

Longword1 (32 bits)

LW1 drive after LW0

Longword0 ((32 bits)

LW0 drive first

PCI Add[2]=1

PCI Add[2]=0

Table 137. Byte Lane Alignment for 32-Bit PCI Data Out (Big-Endian to 32 Bits PCI Big-Endian

without Swap)

SRAM Data

IN[7:0]

IN[15:8]

IN[23:16]

IN[31:24]

IN[7:0]

IN[15:8]

IN[23:16]

IN[31:24]

Longword1 (32 bits)

LW1 drive after LW0

Longword0 ((32 bits)

LW0 drive first

DRAM Data

IN[39:32]

IN[47:40]

IN[55:48]

IN[63:56]

IN[7:0]

IN[15:8]

IN[23:16]

IN[31:24]

PCI Data

OUT[7:0]

OUT[15:8]

OUT[23:16]

OUT[31:24]

OUT[7:0]

OUT[15:8]

OUT[23:16]

OUT[31:24]

Longword1 (32 bits)

LW1 drive after LW0

Longword0 ((32 bits)

LW0 drive first

PCI Add[2]=1

PCI Add[2]=0