130 overall clock generation and distribution, 147 clock usage summary, Figure 130 – Intel NETWORK PROCESSOR IXP2800 User Manual

Page 360: Show, Table 147, Intel

360

Hardware Reference Manual

Intel

®

IXP2800 Network Processor

Clocks and Reset

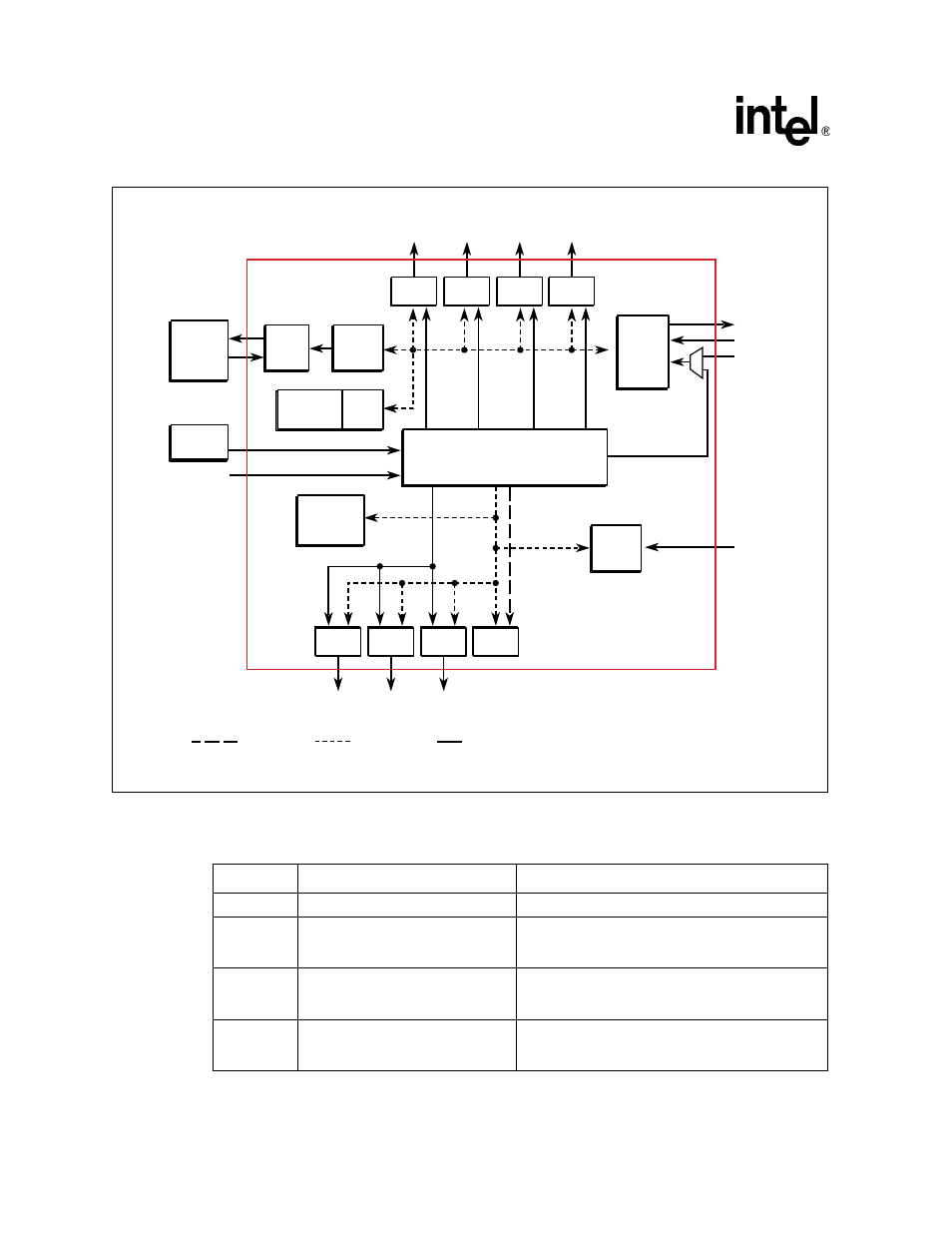

Figure 130. Overall Clock Generation and Distribution

A9777-02

Scratch,

Hash,

CSR

PCI

Slow Port

Devices,

i.e., Flash,

ROM

Peripherals

(Timers,

UART, etc.)

External

Oscillator

Constant

(Multiplier)

SRAM2

SRAM3

SRAM1

SRAM0

S_clk2

S_clk3

S_clk1

S_clk0

Media

and

Switch

Fabric

Interface

Clock Unit with PLL

tdclk

rdclk

PCI_clk

tclk_ref

Slow

Port

Control

Gasket

ref_clk_l

ref_clk_h

Intel

XScale

®

Core

DRAM2

MEs

DRAM1

DRAM0

D_clk2

D_clk1

D_clk0

Key:

Fast Clock

½ Fast Clock

Divided Clock

Intel

®

IXP2800

Network Processor

Table 147. Clock Usage Summary (Sheet 1 of 2)

Unit Name

Description

Comment

Microengine

Microengines internal.

Internal

Buses

Command/Push/Pull interface of

DRAM, SRAM, Intel XScale

®

core,

Peripheral, MSF, and PCI Units.

1/2 Microengine frequency.

Intel

XScale

®

core

Intel XScale

®

core microprocessor,

caches, microprocessor side of

Gasket.

1/2 of Microengine frequency.

DRAM

DRAM pins and control logic (all of

DRAM unit except Internal Bus

interface).

Divide of Microengine frequency. All DRAM channels

use the same frequency. Clocks are driven by the

IXP2800 Network Processor to external DRAMs.