4 support for hybrid simplex operation, 115 reference model for hybrid simplex operation, Support for hybrid simplex operation – Intel NETWORK PROCESSOR IXP2800 User Manual

Page 307

Hardware Reference Manual

307

Intel

®

IXP2800 Network Processor

Media and Switch Fabric Interface

The transfer time of CFrames across the RPCI is four times that of the data interface. The latency

of link-level flow control notifications depends on the frequency of sending new CFrame base

headers. As such, the maximum size of CFrames supported on the RPCI should be limited to

provide sufficient link-level flow control responsiveness.

The behavior of state machines for a full-duplex interface regarding interface initialization, link-

level flow control, and requests to send a de-skew training sequence is supported by the data

interface in combination with its reverse path control interface as if the two interfaces were

equivalent to a full-duplex interface.

The simplex mode of interfacing to the ingress and egress network processor is an alternative to the

dual chip full-duplex configuration. It provides earlier notification of Flow Control CFrame

congestion within the ingress network processor and marginally less latency for delivery of Flow

Control CFrames to the ingress network processor. It allows more of the bandwidth on the data

interface to be used for the transfer of data CFrames as Flow Control CFrames are transferred on

the RPCI.

The simplex configuration provides a straightforward mechanism for the egress network processor

to send VOQ flow control to the fabric if the fabric supports such functionality. In the dual chip,

full-duplex configuration, the egress network processor sends a request across the PCI to the

ingress network processor, requesting that a Flow Control CFrame be sent to the fabric.

8.9.4.2.4

Support for Hybrid Simplex Operation

The SPI-4.2 interface may be used to transfer data to and from a fabric, although there is no

standard protocol for such conveyance. The necessary addressing information for the fabric and

egress network processor may be encoded within the address bits of the preceding control word or

stored in the initial data words of the SPI-4.2 burst. The LVTTL status interface may be used to

provide link-level flow control for the data bursts. (The SPI-4.2 LVDS status interface cannot be

used, because it shares the same pins with the fabric flow control interface.)

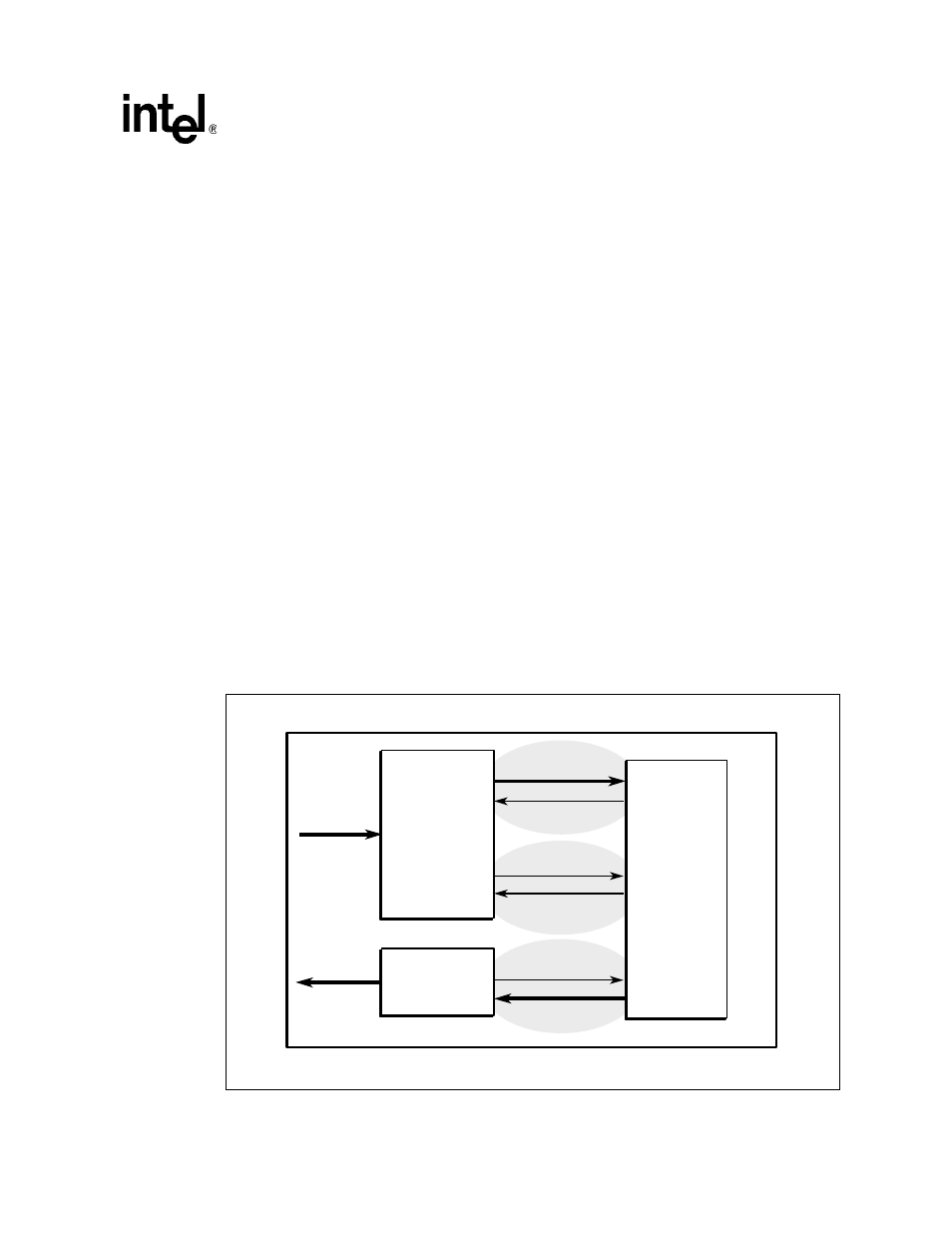

Figure 115. Reference Model for Hybrid Simplex Operation

B2753-01

Back Pressure

Flow Control

Interface

Fabric

Interface

Chip(s)

Printed Circuit Card

SPI-4.2 Data

Interface

SPI-4.2

Data Interface

SPI-4.2 Status

Interface

SPI-4.2

Status Interface

Egress

Network

Processor

Ingress

Network

Processor