2 csix, Csix, 101 transmit csix header – Intel NETWORK PROCESSOR IXP2800 User Manual

Page 269

Hardware Reference Manual

269

Intel

®

IXP2800 Network Processor

Media and Switch Fabric Interface

If the next sequential element is not valid when its turn comes up:

1. Send an idle Control Word with SOP set to 0, and EOPS set to the values determined from the

most recently sent element, ADR field 0x00, correct parity.

2. Until an element becomes valid, send idle Control Words with SOP set to 0, EOPS set to 00,

ADR field 0x00, and correct parity.

Note: Sequential elements with same ADR are not “merged”, a Control Word is sent for each element.

Note: SPI-4 requires that all data transfers, except the last fragment (with EOP), be multiples of 16 bytes.

It is up to the software loading the TBUF element to enforce this rule.

After an element has been sent on the transmit pins, the valid bit for that element is cleared. The

Tx_Sequence register is incremented when the element has been transmitted; by also maintaining

a sequence number of elements that have been allocated (in software), the microcode can

determine how many elements are in-flight.

8.3.3.2

CSIX

Transmit control logic sends valid elements on the transmit pins in element order. Each element

sends a single CFrame. First the Base Header is sent — it is formed as shown in

. Next,

the Extension Header is sent. Finally, the data is sent; the number of bytes to send is the total of

Element Control Word Prepend Length field plus the Element Control Word Payload Length, plus

padding to fill the final CWord if required (the CWord Size is programmed in

MSF_Tx_Control[Tx_CWord_Size]). Both Horizontal Parity and Vertical Parity are transmitted, as

described in

.

Note: When transmitting a Flow Control CFrame, the entire payload must be written into the TBUF

entry. The extension header field of the Transmit Control Word is not used for Flow Control

CFrames.

Control elements and Data elements share use of the transmit pins. Each will alternately transmit a

valid element, if present.

If the next sequential element is not valid when its turn comes up, or if transmission is disabled by

FC_Ingress_Status[SF_CReady] or FC_Ingress_Status[SF_DReady], then transmit logic will

alternate sending Idle CFrames with Dead Cycles; it will continue to do so until a valid element is

ready. Idle CFrames get the value for the Ready Field from FC_Ingress_Status[TM_Cready] and

FC_Ingress_Status[TM_DReady], the Payload Length is set to 0.

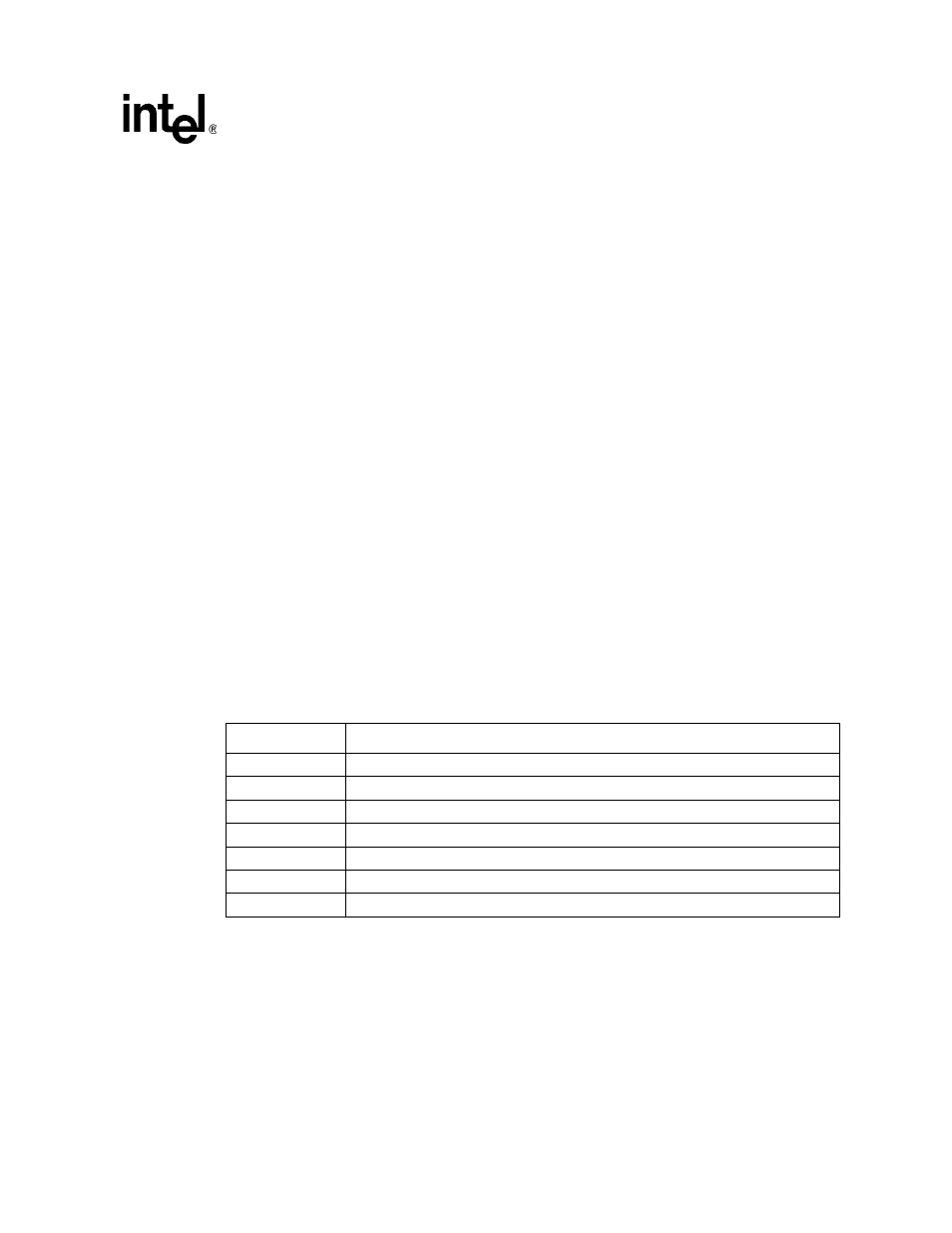

Table 101. Transmit CSIX Header

CSIX Header Field

Derived From

Type

Type field of Element Control Word

Data Ready

FC_Ingress_Status[TM_DReady]

Control Ready

FC_Ingress_Status[TM_CReady]

Payload Length

Element Control Word Prepend Length + Element Control Word Payload Length

P

P Bit of Element Control Word

CR

CR Bit of Element Control Word

Extension Header

Extension Header field of Element Control Word