2 virtual output queue, 8 parity, 1 spi-4 – Intel NETWORK PROCESSOR IXP2800 User Manual

Page 260: Parity 8.2.8.1, Spi-4, 93 extent of dip-4 codes, Section 8.2.8.1

260

Hardware Reference Manual

Intel

®

IXP2800 Network Processor

Media and Switch Fabric Interface

8.2.7.2.2

Virtual Output Queue

CSIX protocol provides Virtual Output Queue Flow Control via Flow Control CFrames. CFrames

that were mapped to FCEFIFO (via the CSIX_Type_Map CSR) are parsed by the receive control

logic and placed into FCEFIFO, which provides buffering while they are sent from the Egress

IXP2800 Network Processor to the Ingress IXP2800 Network Processor over the TXCDAT signals

(normally Flow Control CFrames would be mapped to FCEFIFO).

The entire CFrame is sent over TXCDAT, including the Base Header and Vertical Parity field. The

32-bit CWord is sent four bits at a time, most significant bits first. The CFrames are forwarded in a

“cut-through” manner, meaning that the Egress IXP2800 Network Processor does not wait for the

entire CFrame to be received before forwarding (each CWord can be forwarded as it is received).

If FCEFIFO gets full, as defined by HWM_Control[FCEFIFO_HWM], then the

FC_Egress_Status[TM_CReady] bit will be deasserted (to inform the Ingress IXP2800 Network

Processor to deassert Control Ready in CFrames sent to the Switch Fabric).

describes how Flow Control information is used in the Ingress IXP2800 Network Processor.

8.2.8

Parity

8.2.8.1

SPI-4

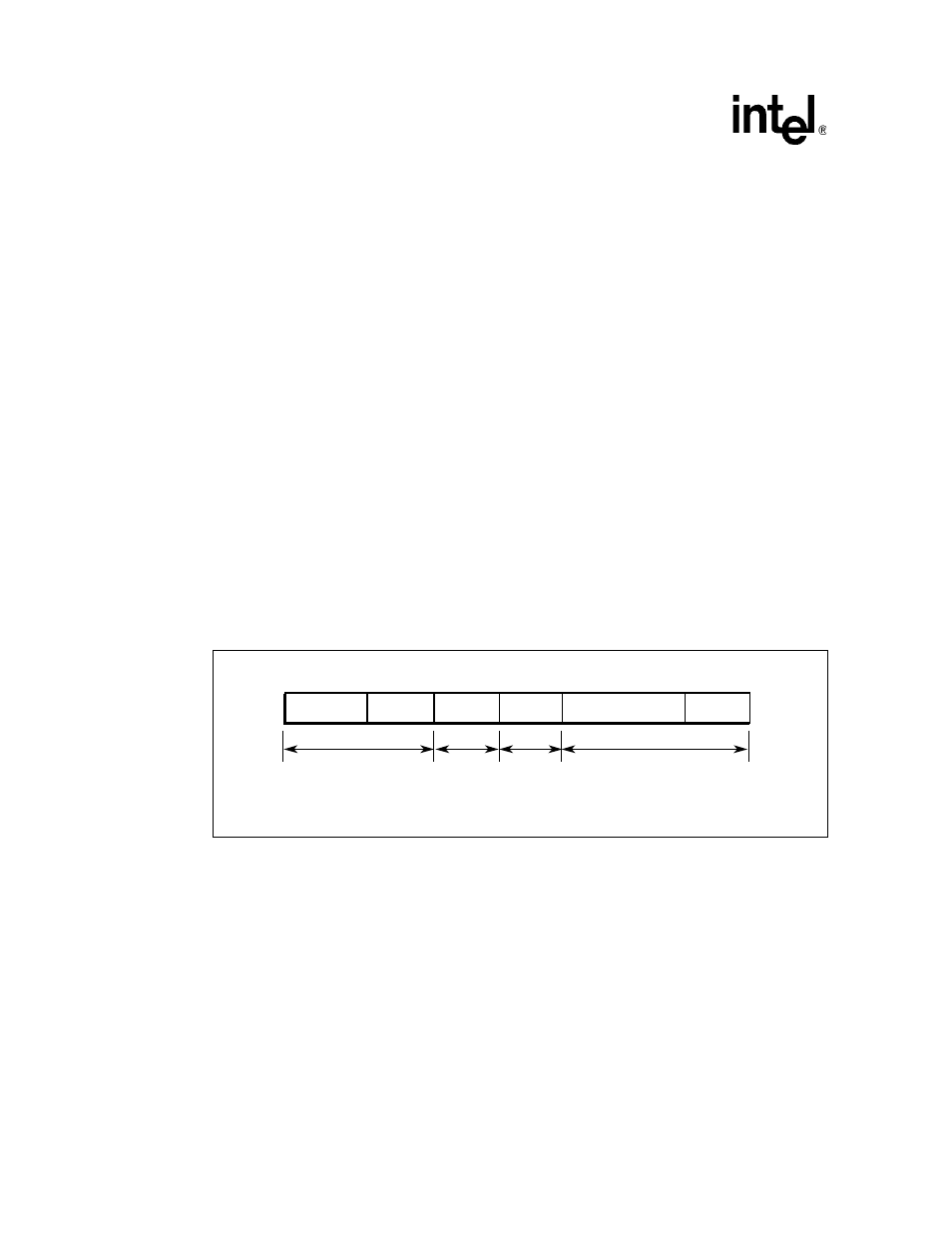

The receive logic computes 4-bit Diagonal Interleaved Parity (DIP-4) as specified in the SPI-4

specification. The DIP-4 field received in a control word contains odd parity computed over the

current Control Word and the immediately preceding data words (if any) following the last Control

Word.

shows the extent of the DIP-4 codes.

There is a DIP-4 Error Flag and a 4-bit DIP-4 Accumulator register. After each Control Word is

received, the Flag is conditionally reset (see Note below this paragraph) and the Accumulator

register is cleared. As each Data Word (if any), and the first succeeding Control Word is received,

DIP-4 parity is accumulated in the register, as defined in the SPI-4 spec. The accumulated parity is

compared to the value received in the DIP-4 field of that first Control Word. If it does not match,

the DIP-4 Error Flag is set. The value of the flag becomes the element status Par Err bit.

Note: An error in the DIP-4 code invalidates the transfers before and after the Control Word, since the

control information is assumed to be in error. Therefore the DIP-4 Error Flag is not reset after a

Control Word with bad DIP-4 parity. It is only reset after a Control Word with correct DIP-4 parity.

Figure 93. Extent of DIP-4 Codes

A9342-01

Payload

Control

Payload

DIP-4 Extent

(between arrows)

Control

Control

Control