Table 63, In th – Intel NETWORK PROCESSOR IXP2800 User Manual

Page 192

192

Hardware Reference Manual

Intel

®

IXP2800 Network Processor

DRAM

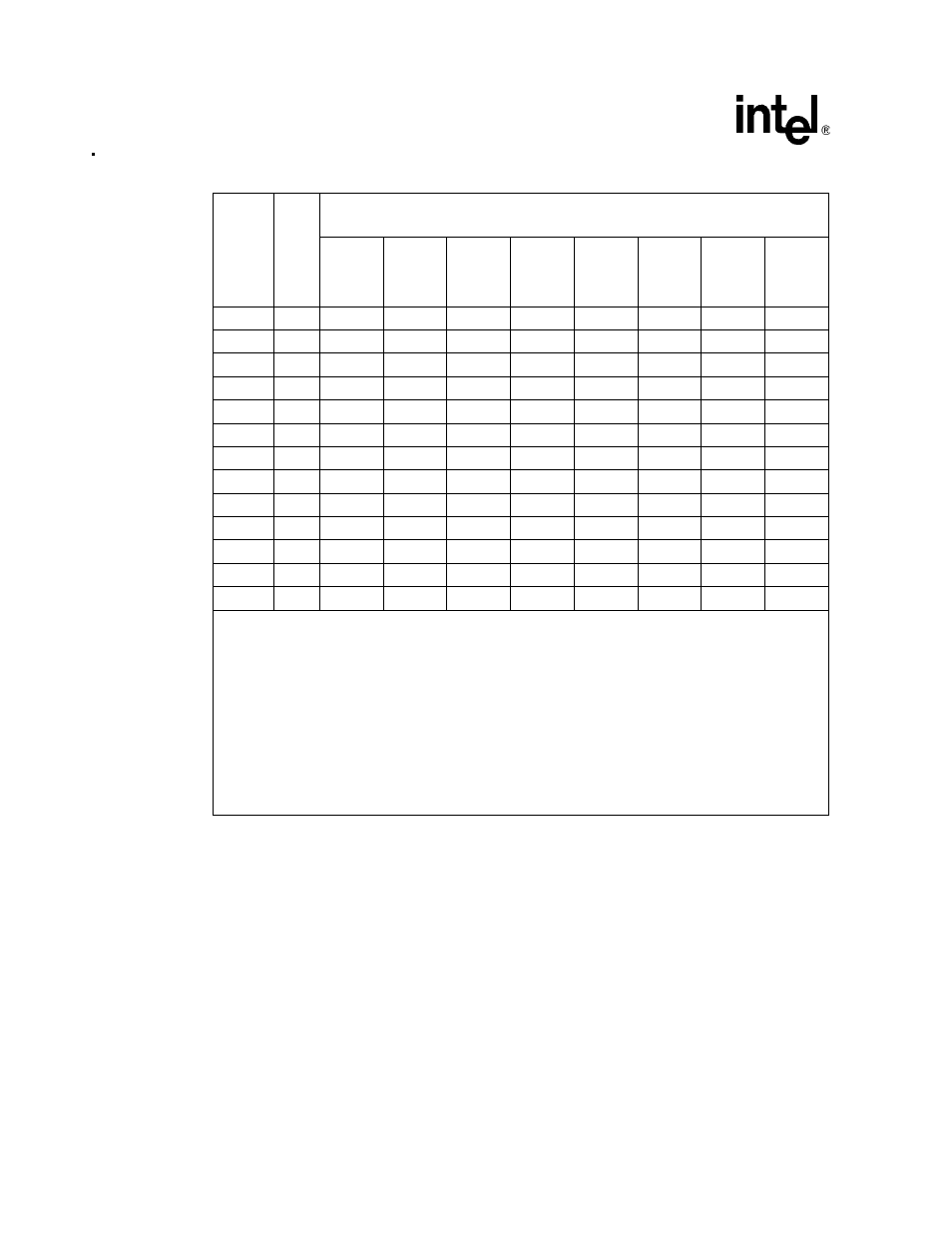

Table 63. Address Rearrangement for 3-Way Interleave (Sheet 1 of 2)

When

these

bits of

address

are all

“1”s…

Shift

30:7

right

by

this

many

bits

Add this amount to shifted 30:7 (based on amount of memory on the channel)

Address within channel is {30:7+table_value), 6:0}

8 MB

3

16 MB

32 MB

3

64 MB

128 MB

3

256 MB

512 MB

3

1 GB

30:7

26

N/A

2

N/A

N/A

N/A

N/A

N/A

N/A

8388607

28:7

24

N/A

N/A

N/A

N/A

N/A

2097151

4194303

8388606

26:7

22

N/A

N/A

N/A

524287

1048575

2097150

4194300

8388600

24:7

20

N/A

131071

262143

524286

1048572

2097144

4194288

8388576

22:7

18

65535

131070

262140

524280

1048560

2097120

4194240

8388480

20:7

16

65532

131064

262128

524256

1048512

2097024

4194048

8388096

18:7

14

65520

131040

262080

524160

1048320

2096640

4193280

8386560

16:7

12

65472

130944

261888

523776

1047552

2095104

4190208

8380416

14:7

10

65280

130560

261120

522240

1044480

2088960

4177920

8355840

12:7

8

64512

129024

258048

516096

1032192

2064384

4128768

8257536

10:7

6

61440

122880

245760

491520

983040

1966080

3932160

7864320

8:7

4

49152

98304

196608

393216

786432

1572864

3145728

6291456

None

2

0

0

0

0

0

0

0

0

NOTES:

1. This is a priority encoder; when multiple lines satisfy the condition, the line with the largest number of ones

is used.

2. N/A means not applicable.

3. For these cases, the top 3 blocks (each block is 128 bytes) of the logical address space is not accessible.

For example if each channel has 8 Mbytes, only (24 Mbytes - 384) total bytes are usable. This is an artifact

of the remapping method.

4. The numbers in the table are derived as follows:

For the first pair of ones (8:7) value is 3/4 the number of blocks. For each subsequent pair of ones, the

value is the previous value, plus another 3/4 the remaining blocks.

• [8:7]==11 - 3/4 * blocks

• [10:7]==1111 - (3/4 + 3/16) * blocks

• [12:7]==111111 - (3/4 + 3/16 + 3/64) * blocks

• etc.