Intel NETWORK PROCESSOR IXP2800 User Manual

Page 126

126

Hardware Reference Manual

Intel

®

IXP2800 Network Processor

Intel XScale

®

Core

The Intel XScale

®

core coprocessor bus is not used in the IXP2800 Network Processors, therefore

all accesses are only through the Command Memory Bus.

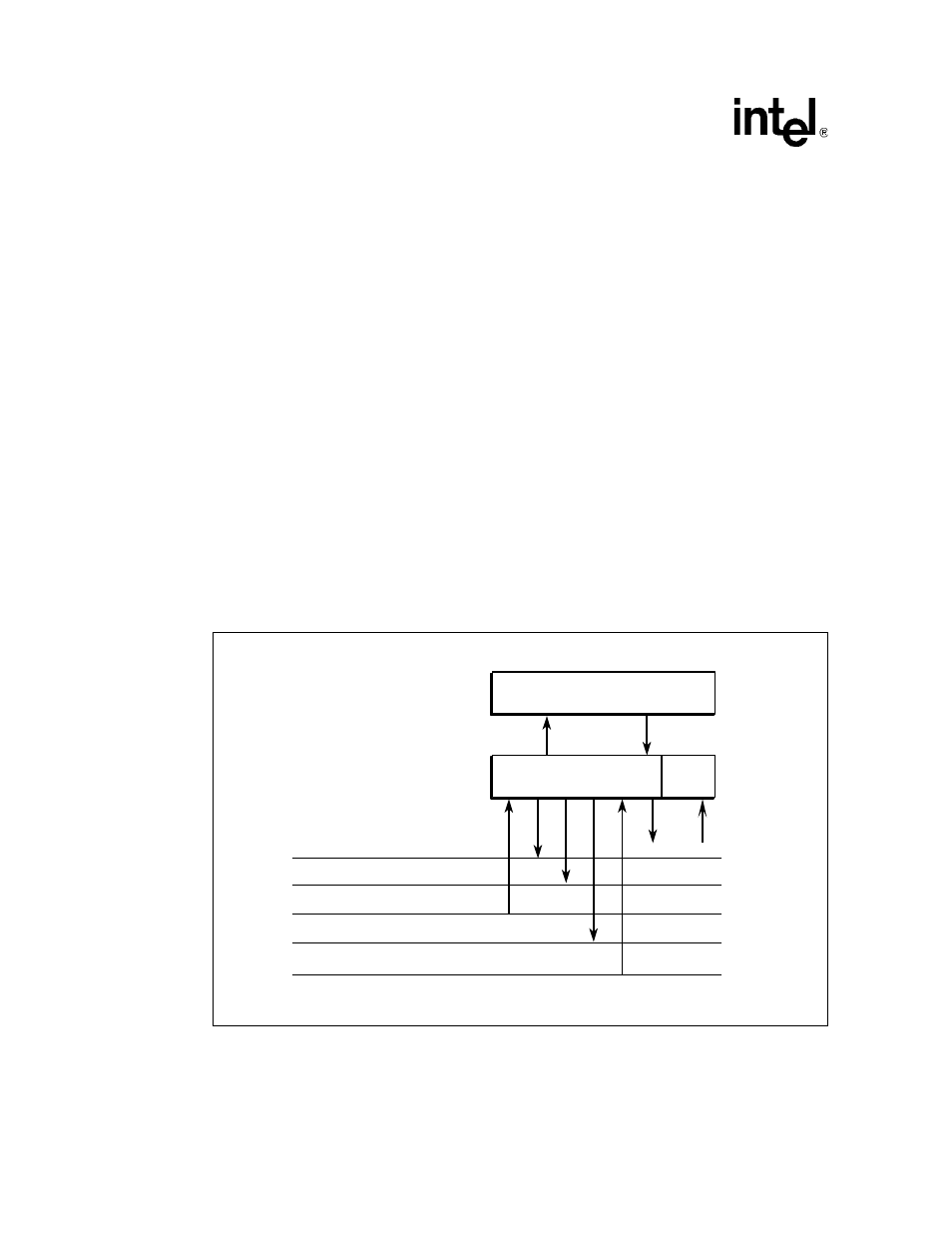

shows the block diagram of the global bus connections to the gasket.

The gasket unit has the following features:

•

Interrupts are sent to the Intel XScale

®

core via the gasket, with the interrupt controller

registers used for masking the interrupts.

•

The gasket converts CMB reads and writes to CPP format.

•

All the atomic operations are applied on SRAM and SCRATCH only, not DRAM.

•

There is a stepping-stone sitting between the Intel XScale

®

core and the gasket. The Intel

XScale

®

core runs at 600 – 700 MHz. The gasket currently supports a 1:1 (IXP2800 Network

Processor) clock ratio. For a 2:1 ratio, the Command Push Pull bus will be running at ½ of the

frequency of the Intel XScale

®

core.

•

In IXP2800 memory controllers, read after write ordering is enforced. There is no write after

read enforcement for the Intel XScale

®

core. The gasket will perform enforcement by

employing Content Addressable Memory (CAM) to detect a write to an address with read

pending. This only applies for writes to SRAM.

•

The gasket CPP interface contains one command bus, one D_Push bus, one D_Pull bus, one

S_Push bus, and one S_Pull bus, each with a 32-bit data width.

A maximum four outstanding reads and four outstanding writes from the Intel XScale

®

core are

allowed.

Figure 27. Global Buses Connection to the Intel XScale

®

Core Gasket

A9697-03

Req

CAP CSR

Intel XScale

®

Core

Gasket

Local

CSR

CMD_BUS

DRAM_PUSH_BUS

SRAM_PULL_BUS

DRAM_PULL_BUS

SRAM_PUSH_BUS