83 spi-4 control word format – Intel NETWORK PROCESSOR IXP2800 User Manual

Page 244

244

Hardware Reference Manual

Intel

®

IXP2800 Network Processor

Media and Switch Fabric Interface

Control words are inserted only between burst transfers; once a transfer has begun, data words are

sent uninterrupted until either End of Packet or a multiple of 16 bytes is reached. The order of bytes

within the SPI-4 data burst is shown in

.

The most significant bits of the bytes correspond to bits 15 and 7. On data transfers that do not end

on an even byte-boundary, the unused byte on bits [7:0] is set to all zeros.

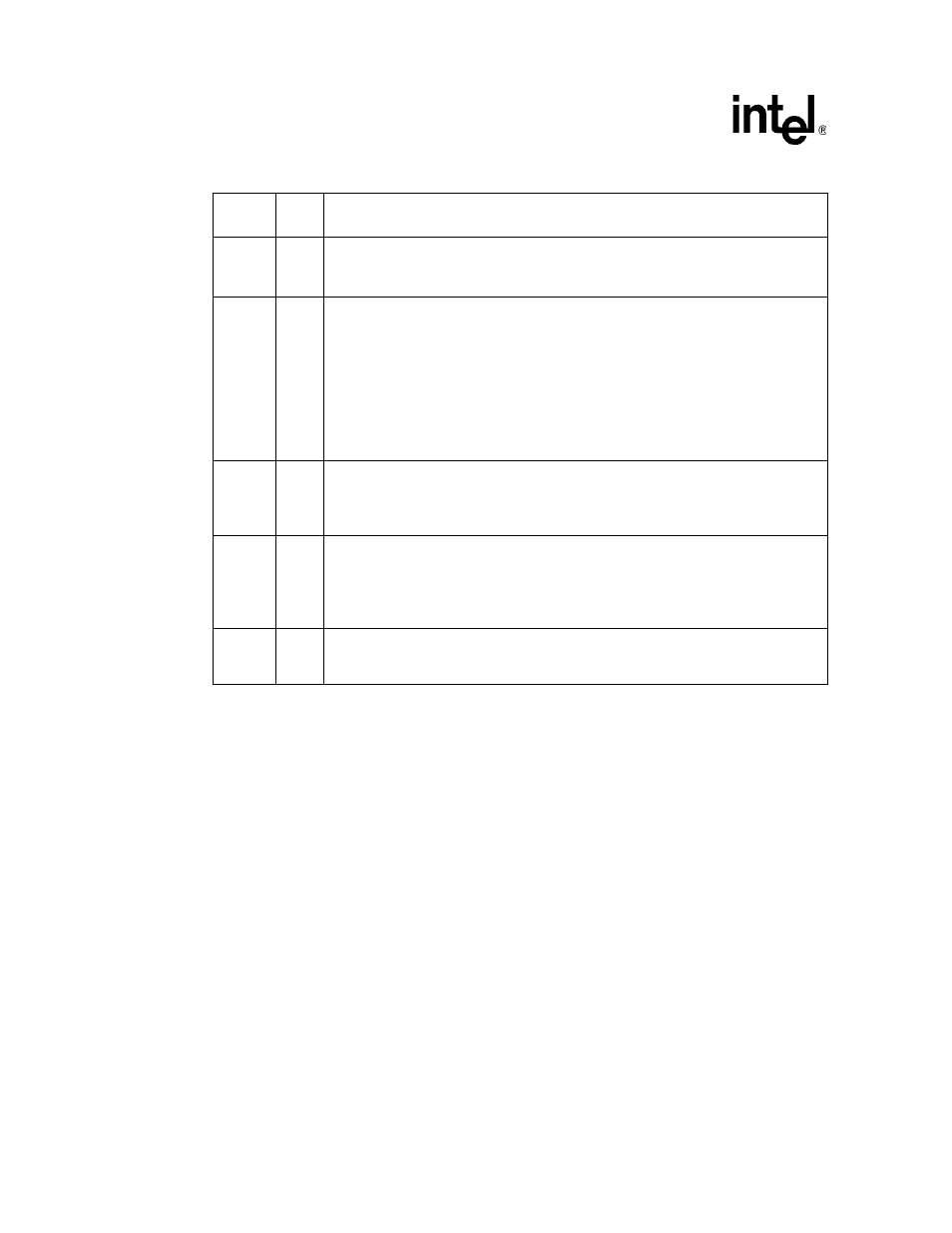

Table 83. SPI-4 Control Word Format

Bit

Position

Label

Description

15

Type

Control Word Type.

• 1—payload control word (payload transfer will immediately follow the control word).

• 0—idle or training control word.

14:13

EOPS

End-of-Packet (EOP) Status.

Set to the following values below according to the status of the immediately preceding

payload transfer.

• 00—Not an EOP.

• 01—EOP Abort (application-specific error condition).

• 10—EOP Normal termination, 2 bytes valid.

• 11—EOP Normal termination, 1 byte valid.

EOPS is valid in the first Control Word following a burst transfer. It is ignored and set to 00

otherwise.

12

SOP

Start-of-Packet (SOP).

• Set to 1 if the payload transfer immediately following the Control Word corresponds to

the start of a packet; set to 0 otherwise.

• Set to 0 in all idle and training control words.

11:4

ADR

Port Address.

8-bit port address of the payload data transfer immediately following the Control Word.

None of the addresses are reserved (all are available for payload transfer).

• Set to all zeros in all idle Control Words.

• Set to all ones in all training Control Words.

3:0

DIP-4

4-bit Diagonal Interleaved Parity.

4-bit odd parity computed over the current Control Word and the immediately preceding

data words (if any) following the last Control Word.