3 command bus master direct access to pci bus, 1 pci address generation for io and mem cycles, Command bus master access to local control and – Intel NETWORK PROCESSOR IXP2800 User Manual

Page 346: Status registers, Command bus master direct access to pci bus, Intel, Ixp2800 network processor pci unit, The intel xscale, 346 hardware reference manual

346

Hardware Reference Manual

Intel

®

IXP2800 Network Processor

PCI Unit

9.4.2.2

Command Bus Master Access to Local Control and

Status Registers

These are CSRs within the PCI Unit that are accessible from push/pull bus masters. The masters

include the Intel XScale

®

core, Microengines. There is no PCI bus cycles generated. The CSRs

within the PCI Unit can be accessed internally by external PCI devices.

9.4.2.3

Command Bus Master Direct Access to PCI Bus

The Intel XScale

®

core and Microengines are the only command bus masters that have direct

access to the PCI bus as a PCI Bus initiator. The PCI Bus can be accessed by push/pull command

bus access to PCI bus address space. The PCI Unit will share the internal SRAM push/pull data bus

with SRAM for the data transfers.

Data from the SRAM push/pull data bus is transferred through the master data port of the FBus

interface of the PCI core. The PCI Core handles all of the PCI Bus protocol handshakes. The

SRAM pull data received for a write command will be transferred to the Master write FIFO for PCI

writes. For PCI reads, data is transferred from the read FIFO to the SRAM push data bus. A 32-

byte Direct buffer is used to support up to 32 bytes of data responses to the direct access to PCI

Bus.

The Command Bus Master access to the PCI bus will require internal arbitration to gain access to

the data FIFOs inside the core, which are shared between the DMA engine and direct access to

PCI.

9.4.2.3.1

PCI Address Generation for IO and MEM Cycles

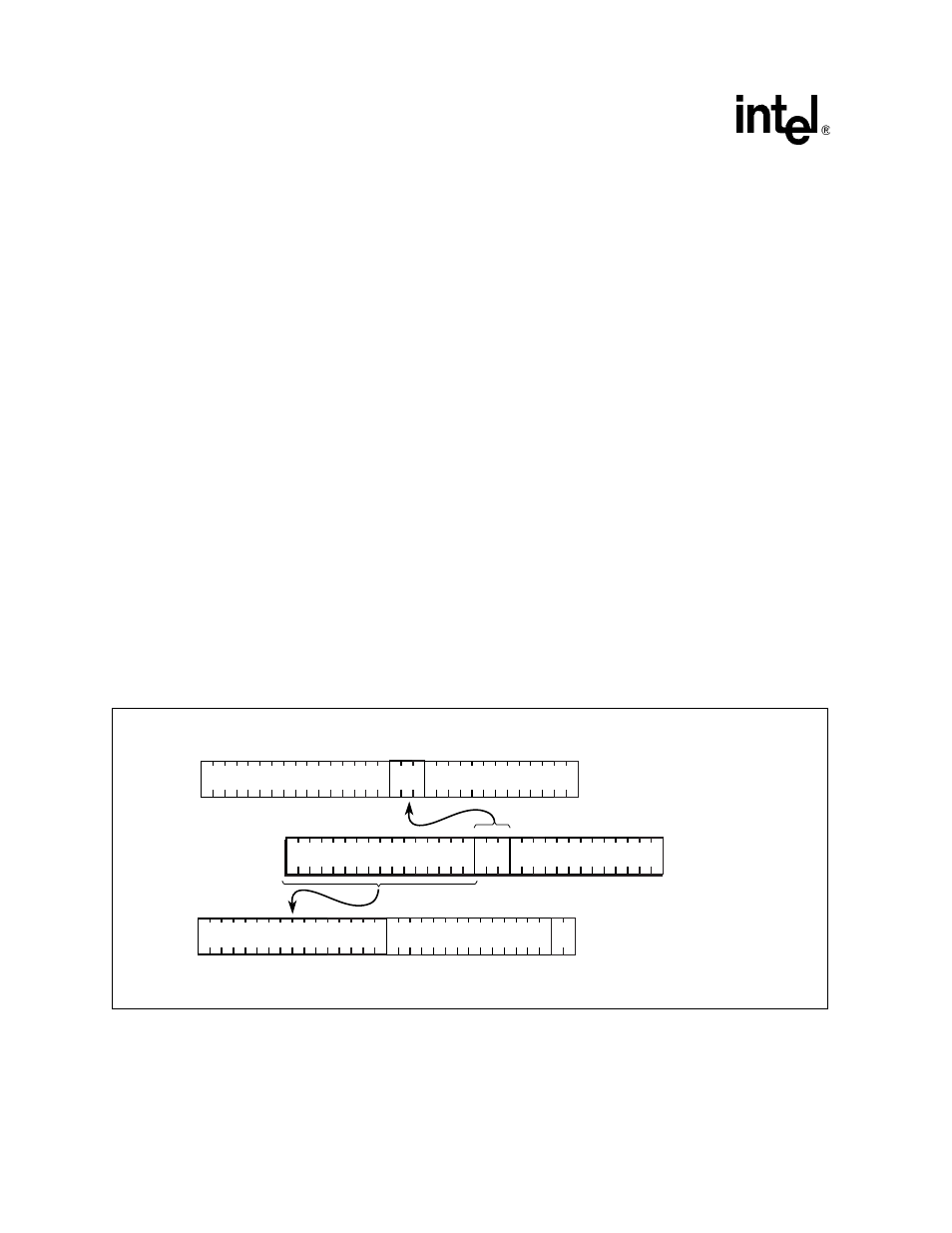

When the push/pull command bus master is accessing the PCI Bus, the PCI address is generated

based on the PCI address extension register (PCI_ADDR_EXT).

shows how the

address is generated from a Command Bus Master address.

Figure 128. PCI Address Generation for Command Bus Master to PCI

A9775-02

31

26

27

28

29

30

23

24

25

19

20

21

22

15

16

17

18

12

14

13

8

9

10

11

4

5

6

7

3

2

1

0

PMSA

PCI Extension

Register

PCI Address for PCI

Memory Accesses

PIOADD

RES

31

26

27

28

29

30

23

24

25

19

20

21

22

15

16

17

18

12

14 13

8

9

10

11

4

5

6

7

3

2

1

0

PCI Address for

PCI I/O Accesses

PIOADD

00

31

26

27

28

29

30

23

24

25

19

20

21

22

15

16

17

18

12

14

13

8

9

10

11

4

5

6

7

3

2

1

0

PMSA

PIOADD

RES

Intel XScale

®

Core Address[15:2]