3 full element list, 4 rx_thread_freelist, Full element list – Intel NETWORK PROCESSOR IXP2800 User Manual

Page 255: Rx_thread_freelist, 92 rx_thread_freelist use, Section 8.2.3, Section 8.2.4

Hardware Reference Manual

255

Intel

®

IXP2800 Network Processor

Media and Switch Fabric Interface

8.2.3

Full Element List

Receive control hardware maintains the Full Element List to hold the status of valid RBUF

elements, in the order in which they were received. When an element is marked valid (as described

for SPI-4 and

for CSIX), its status is added to the tail of the Full

Element List. When a Microengine is notified of element arrival (by having the status written to its

S_Transfer register; see

), it is removed from the head of the Full Element List.

8.2.4

Rx_Thread_Freelist_#

Each Rx_Thread_Freelist_# is a FIFO that indicates Microengine Contexts that are awaiting an

RBUF element to process. This allows the Contexts to indicate their ready-status prior to the

reception of the data, as a way to eliminate latency. Each entry added to a Freelist also has an

associated S_Transfer register and signal number. The receive logic maintains either one, two, or

three separate lists based on MSF_Rx_Control[RBUF_Partition],

MSF_Rx_Control[CSIX_Freelist], and Rx_Port_Map as shown in

.

To be added as ready to receive an element, an Microengine does an

msf[write]

or

msf[fast_write]

to the Rx_Thread_Freelist_# address; the write data is the Microengine/

Context/S_Transfer register number to add to the Freelist. Note that using the data (rather than the

command bus ID) permits a Context to add either itself or other Contexts as ready.

When there is valid status at the head of the Full Element List, it will be pushed to a Microengine.

The receive control logic pushes the status information (which includes the element number) to the

Microengine in the head entry of Rx_Thread_Freelist_#, and sends an Event Signal to the

Microengine. It then removes that entry from the Rx_Thread_Freelist_#, and removes the status

from Full Element List. (Note that this implies the restriction — a Context waiting on status must

not read the S_Transfer register until it has been signaled.) See

for more information.

In the event that Rx_Thread_Freelist_# is empty, the valid status will be held in Full Element List

until an entry is put into Rx_Thread_Freelist_#.

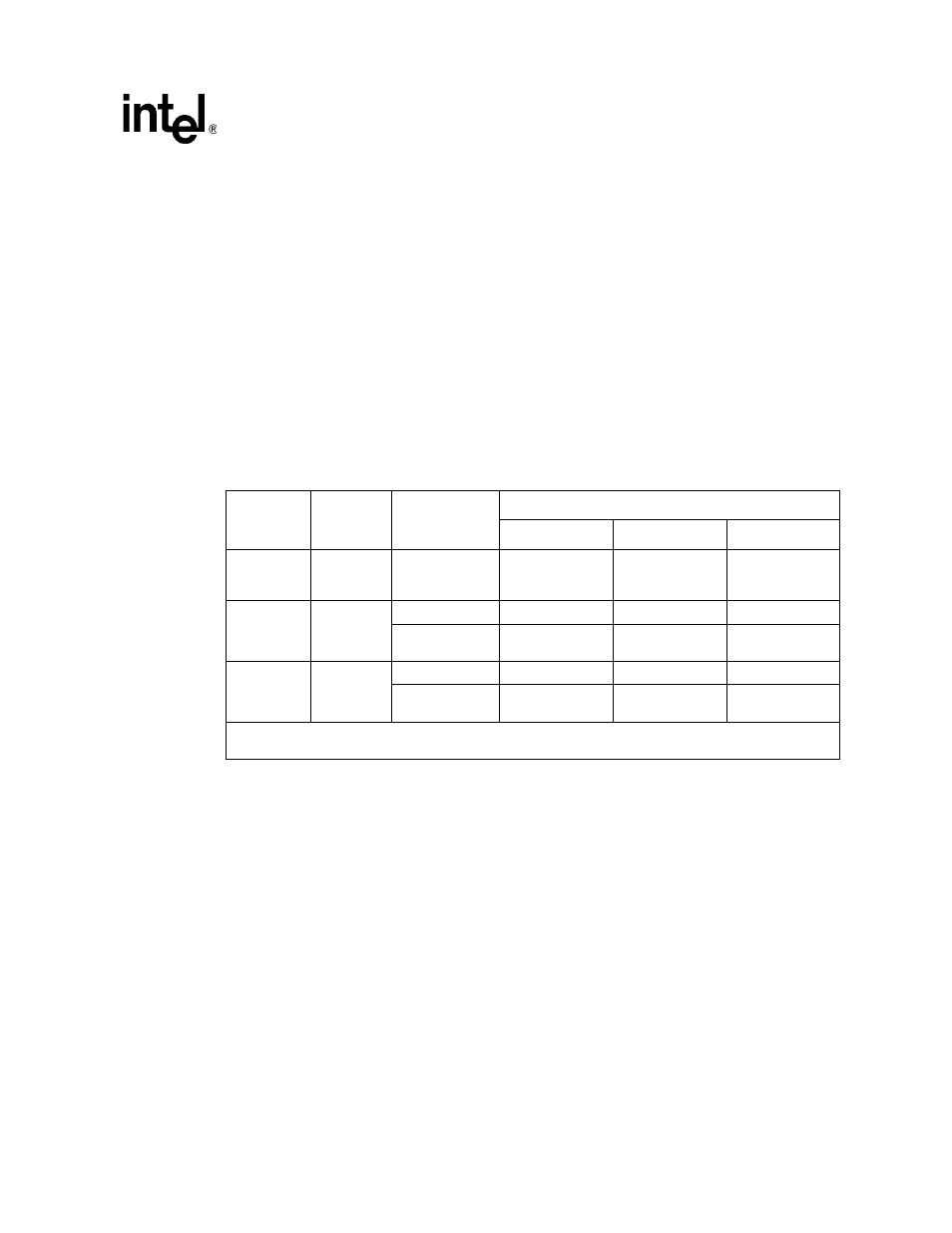

Table 92. Rx_Thread_Freelist Use

Number of

Partitions

Use

CSIX_Freelist

Rx_Thread_Freelist_# Used

0

1

2

1

SPI-4 only

n/a

SPI-4 Ports equal

to or below

Rx_Port_Map

SPI-4 Ports above

Rx_Port_Map

Not Used

2

CSIX only

0

CSIX Data

CSIX Control

Not Used

1

CSIX Data and

CSIX Control

Not Used

Not Used

3

Both SPI-4

and CSIX

0

CSIX Data

SPI-4

CSIX Control

1

CSIX Data and

CSIX Control

SPI-4

Not Used

1. Programmed in MSF_Rx_Control[RBUF_Partition].

2. Programmed in MSF_Rx_Control[CSIX_Freelist].