90 receive and transmit clock generation, 84 order of bytes within the spi-4 data burst – Intel NETWORK PROCESSOR IXP2800 User Manual

Page 245

Hardware Reference Manual

245

Intel

®

IXP2800 Network Processor

Media and Switch Fabric Interface

shows the order of bytes on SPI-4; this example shows a 43-byte packet.

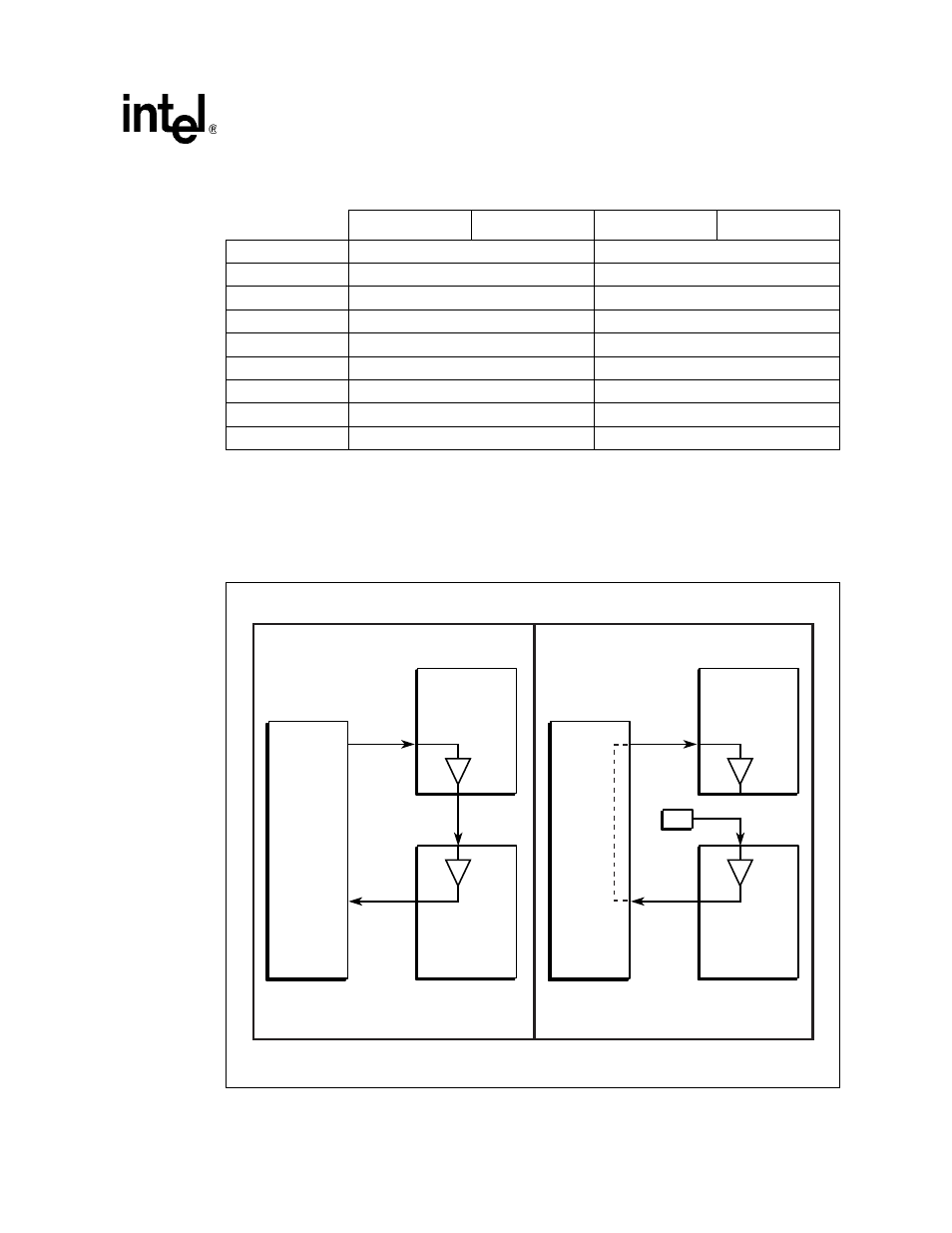

shows two ways in which the SPI-4 clocking can be done. Note that it is also possible to

use an internally-supplied clock and leave TCLK_REF unused.

Table 84. Order of Bytes

1

within the SPI-4 Data Burst

1.

These bytes are valid only if EOP is set.

Bit 15

Bit 8

Bit 7

Bit 0

Data Word 1

Byte 1

Byte 2

Data Word 2

Byte 3

Byte 4

Data Word 3

Byte 5

Byte 5

Data Word 4

Byte 7

Byte 6

…

…

…

…

…

…

…

…

…

Data Word 21

Byte 41

Byte 42

Data Word 22

Byte 43

2

2.

All transfers on the SPI-4 bus must be in multiples of 16 bytes if it is not associated with an End of Packet (EOP) transfer,

to comply with the protocol. Hence, this 43-byte example would only be valid for an EOP transfer.

00

Figure 90. Receive and Transmit Clock Generation

A9760-01

PHY

PHY chip generates RDCLK internally and

supplies it to Ingress Intel

®

IXP2800

Network Processor.

RDCLK

Ingress

IXP2800

Network

Processor

TDCLK

RCLK_REF

TCLK_REF

Egress

IXP2800

Network

Processor

PHY

Oscillator supplies TCLK_REF to Egress

Intel IXP2800 Network Processor, used to

generate TDCLK.

RDCLK

Osc

Ingress

IXP2800

Network

Processor

TDCLK

RCLK_REF

TCLK_REF

Egress

IXP2800

Network

Processor

Ingress IXP2800 Network Processor supplies

RCLK_REF to TCLK_REF, so TDCLK is same

frequency as RDCLK.

PHY uses TDCLK to generate RDCLK to

Ingress IXP2800 Network Processor.

RCLK_REF is not used.