6 write to hash unit, 2 media access, Write to hash unit – Intel NETWORK PROCESSOR IXP2800 User Manual

Page 183: Media access, 62 48-, 64-, and 128-bit hash operand transfers

Hardware Reference Manual

183

Intel

®

IXP2800 Network Processor

Microengines

4.5.1.6

Write to Hash Unit

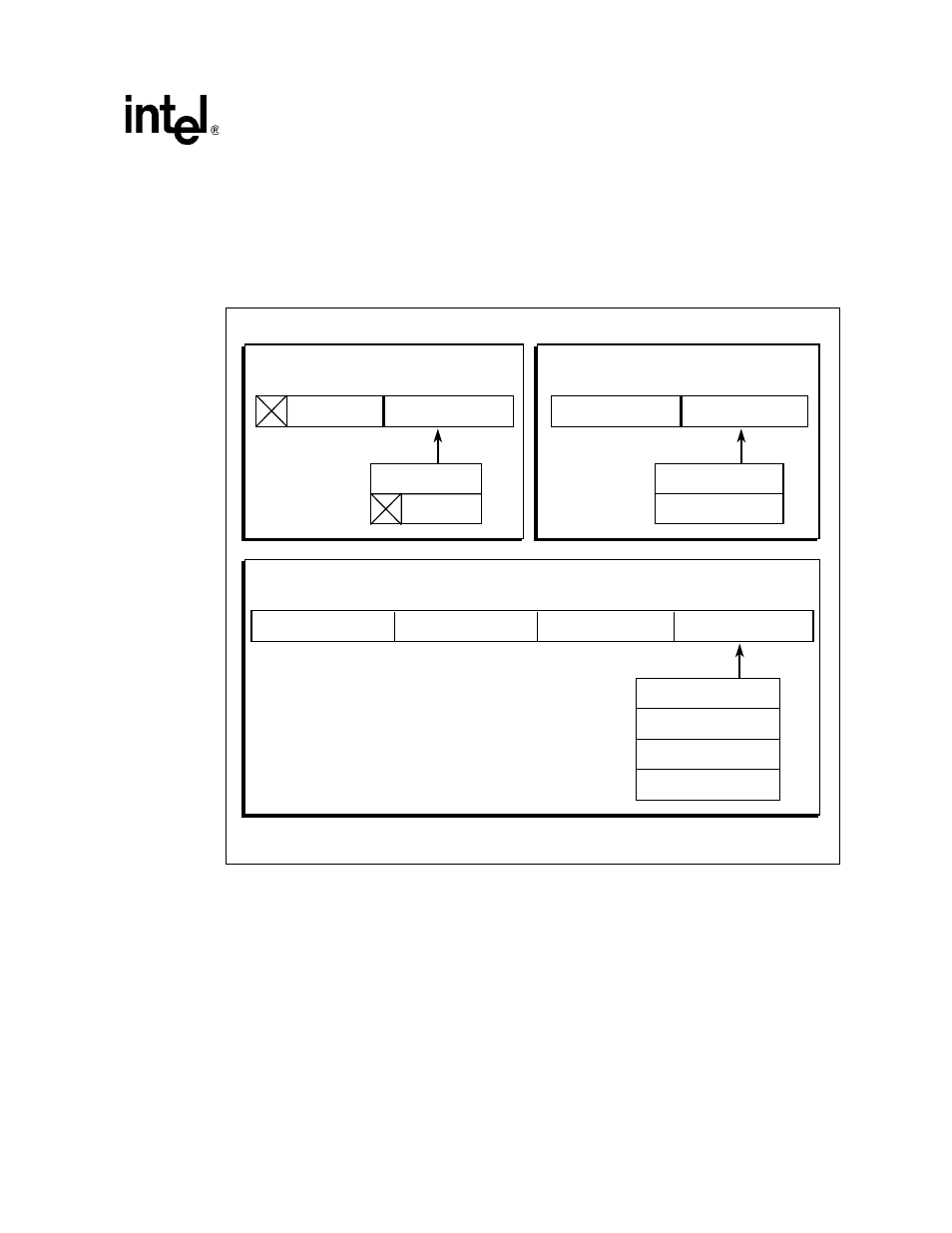

explains 48-, 64-, and 128-bit hash operations. When the Microengine transfers a 48-bit

hash operand to the hash unit, the operand resides in two transfer registers and is transferred, as

shown in

. In the second longword transfer, only the lower half is valid. Hash unit

concatenates the two longwords as shown in

. Similarly, 64-bit and 128-bit hash operand

transfers from the Microengine to the hash unit happen as shown in

4.5.2

Media Access

Media operation can be divided in two parts:

•

Read from RBUF (

•

Write to TBUF (

)

Figure 62. 48-, 64-, and 128-Bit Hash Operand Transfers

A8943-01

63

0

32 31

48-bit Hash

MicroEngine

Transfer Registers

treg0

S-Push / S-Pull Bus

treg1

11 10 9 8

7 6 5 4 3 2 1 0

7 6 5 4 3 2 1 0

11 10 9 8

127

0

96 95

64 63

32 31

128-bit Hash

MicroEngine

Transfer Registers

treg0

S-Push / S-Pull Bus

treg1

treg2

treg3

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

15 14 13 12 11 10 9 8

7 6 5 4 3 2 1 0

7 6 5 4 3 2 1 0

31 30 29 28 27 26 25 24

23 22 21 20 19 18 17 16

15 14 13 12 11 10 9 8

63

0

32 31

64-bit Hash

MicroEngine

Transfer Registers

treg0

S-Push / S-Pull Bus

treg1

7 6 5 4 3 2 1 0

7 6 5 4 3 2 1 0

15 14 13 12 11 10 9 8

15 14 13 12 11 10 9 8