Intel NETWORK PROCESSOR IXP2800 User Manual

Page 403

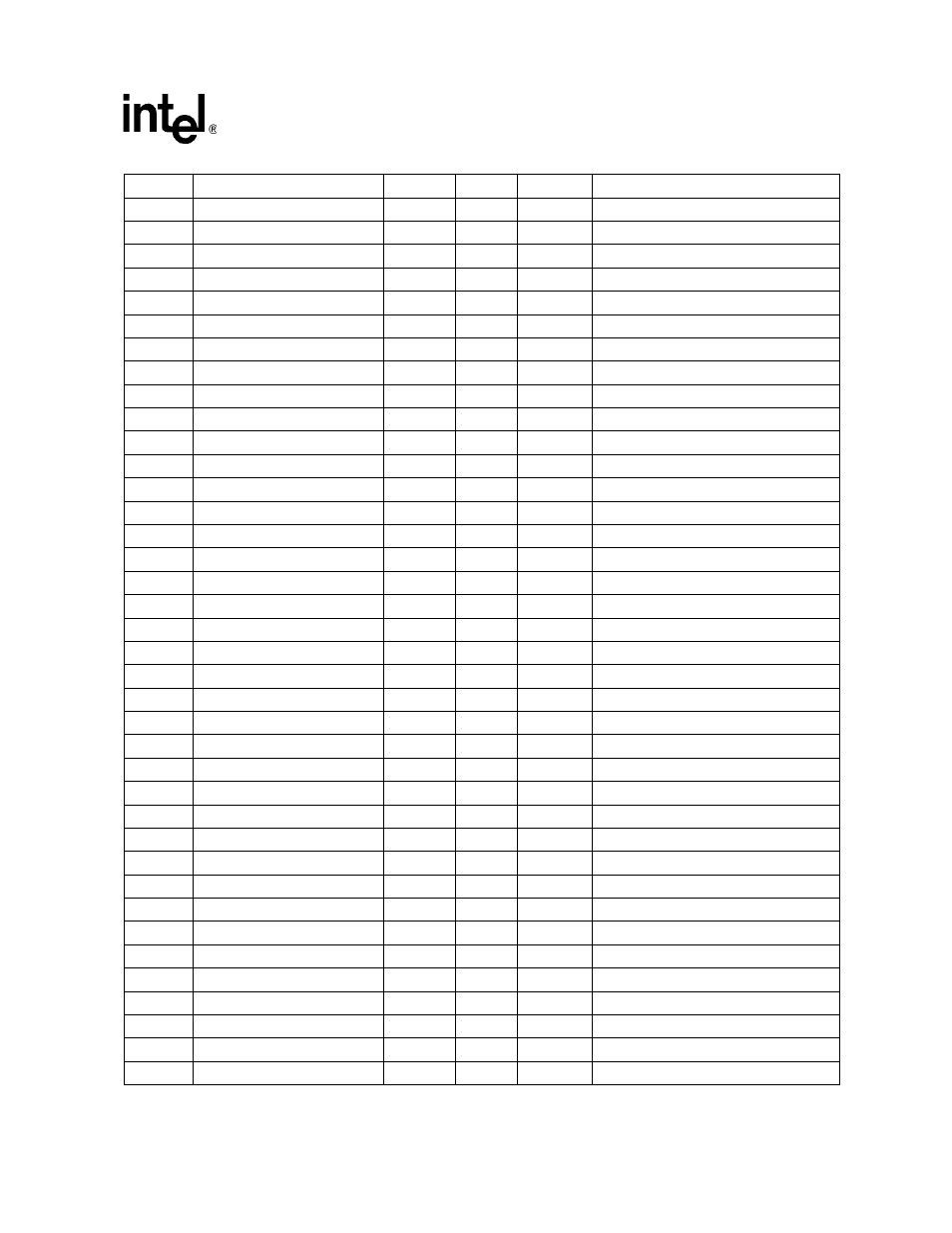

Hardware Reference Manual

403

Intel

®

IXP2800 Network Processor

Performance Monitor Unit

32

reserved

33

reserved

34

XG_CFIFO_EMPTYN_CPP

P_CLK

single

separate

XG command FIFO empty flag

35

XG_DFIFO_EMPTYN_CPP

P_CLK

single

separate

XG DRAM data FIFO empty flag

36

XG_SFIFO_EMPTYN_CPP

P_CLK

single

separate

XG SRAM data FIFO empty flag

37

XG_LCFIFO_EMPTYN_CPP

P_CLK

single

separate

XG lcsr command FIFO empty flag

38

XG_LDFIFO_EMPTYN_CPP

P_CLK

single

separate

XG lcsr data FIFO empty flag

39

reserved

40

XG_OFIFO_EMPTYN_CPP

P_CLK

single

separate

XG cpp command FIFO empty flag

41

XG_OFIFO_FULLN_CPP

P_CLK

single

separate

XG cpp command FIFO full flag

42

XG_DP_EMPTYN_CPP

P_CLK

single

separate

XG DRAM pull data FIFO empty flag

43

XG_SP_EMPTYN_CPP

P_CLK

single

separate

XG SRAM pull data FIFO empty flag

44

XG_HASH_48_CPP

P_CLK

single

separate

hash_48 command on cpp bus

45

XG_HASH_64_CPP

P_CLK

single

separate

hash_64 command on cpp bus

46

XG_HASH_128_CPP

P_CLK

single

separate

hash_128 command on cpp bus

47

XG_LCSR_FIQ_CPP

P_CLK

single

separate

XG FIQ generated by interrupt CSR

48

XG_LCSR_IRQ_CPP

P_CLK

single

separate

XG IRQ generated by interrupt CSR

49

XG_CFIFO_RD_CPP

P_CLK

single

separate

XG command FIFO dequeue

50

XG_DFIFO_RD_CPP

P_CLK

single

separate

XG DRAM data FIFO dequeue

51

XG_SFIFO_RD_CPP

P_CLK

single

separate

XG SRAM data FIFO dequeue

52

XG_LCFIFO_RD_CPP

P_CLK

single

separate

XG lcsr command FIFO dequeue

53

XG_LDFIFO_RD_CPP

P_CLK

single

separate

XG lcsr data FIFO dequeue

54

XG_LCSR_WR_CPP

P_CLK

single

separate

XG lcsr return data FIFO enqueue

55

XG_OFIFO_RD_CPP

P_CLK

single

separate

XG cpp command FIFO dequeue

56

XG_OFIFO_WR_CPP

P_CLK

single

separate

XG cpp command FIFO enqueue

57

XG_DPDATA_WR_CPP

P_CLK

single

separate

XG DRAM pull data FIFO enqueue

58

XG_DPDATA_RD_CPP

P_CLK

single

separate

XG DRAM pull data FIFO dequeue

59

XG_SPDATA_WR_CPP

P_CLK

single

separate

XG SRAM pull data FIFO enqueue

60

XG_SPDATA_RD_CPP

P_CLK

single

separate

XG SRAM pull data FIFO dequeue

61

XG_PUFF0_WR_CPP

P_CLK

single

separate

XG push fifo0 enqueue

62

XG_PUFF1_WR_CPP

P_CLK

single

separate

XG push fifo1 enqueue

63

XG_PUFF2_WR_CPP

P_CLK

single

separate

XG push fifo2 enqueue

64

XG_PUFF3_WR_CPP

P_CLK

single

separate

XG push fifo3 enqueue

65

XG_PUFF4_WR_CPP

P_CLK

single

separate

XG push fifo4 enqueue

66

XG_SRAM_RD_CPP

P_CLK

single

separate

XG SRAM read command on cpp bus

67

XG_SRAM_RD_1_CPP

P_CLK

single

separate

XG SRAM read length=1 on cpp bus

68

XG_SRAM_RD_8_CPP

P_CLK

single

separate

XG SRAM read length=8 on cpp bus

69

XG_SRAM_WR_CPP

P_CLK

single

separate

XG SRAM write command on cpp bus

70

XG_SRAM_WR_1_CPP

P_CLK

single

separate

XG SRAM write length=1 on cpp bus

Table 158. Intel XScale

®

Core Gasket PMU Event List (Sheet 2 of 4)