Intel, Ixp2800 network processor intel xscale, Hardware reference manual 161 – Intel NETWORK PROCESSOR IXP2800 User Manual

Page 161

Hardware Reference Manual

161

Intel

®

IXP2800 Network Processor

Intel XScale

®

Core

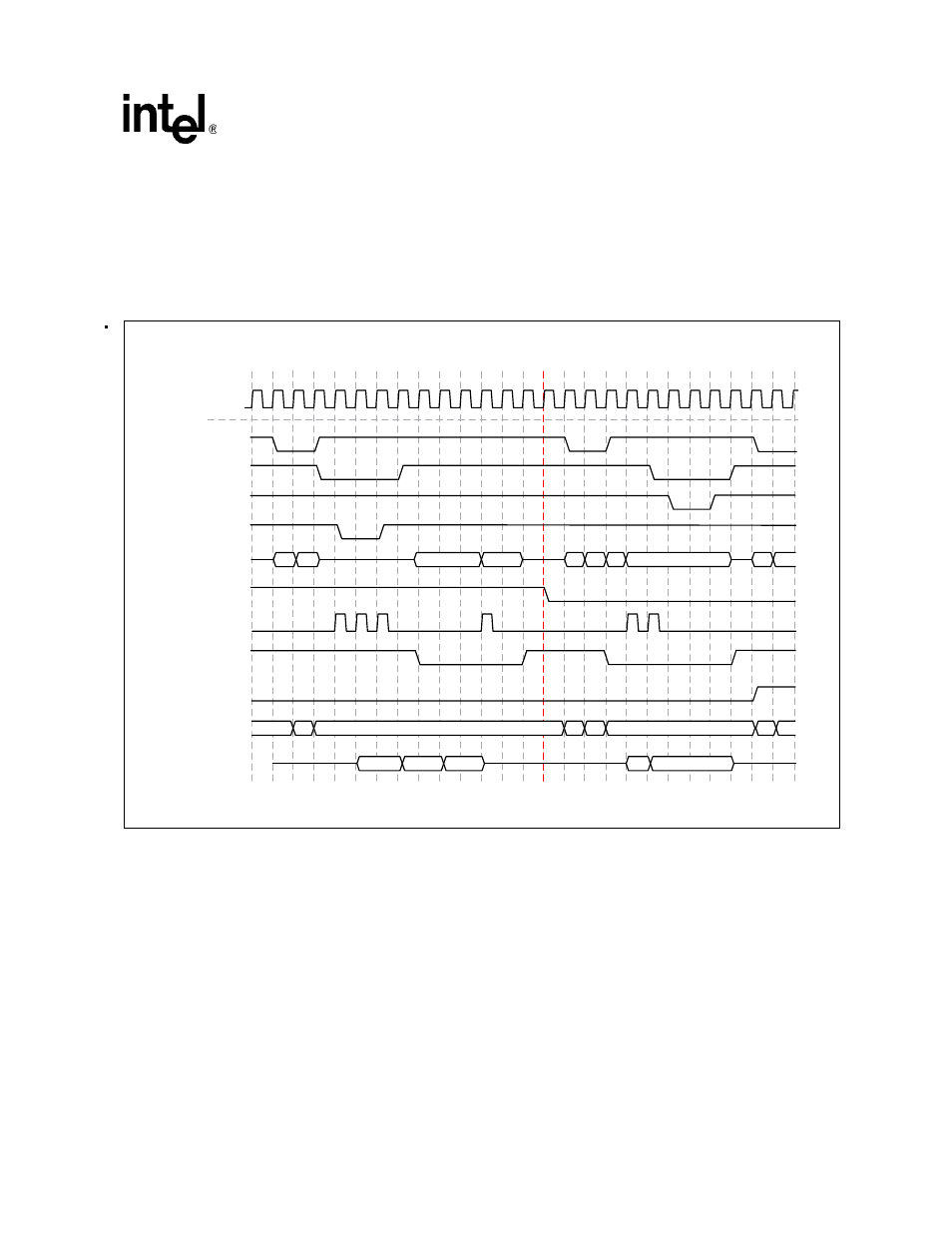

Mode 3 Read Interface Protocol

depicts a single read transaction launched from the IXP2800 to the Intel and AMCC*

SONET/SDH device, followed by two consecutive writes.

Similarly, the access time is much better than the Lucent* TDAT042G5. The access time is eight

clock cycles or 160 ns for a 50-MHz Slowport clock. Here, there are three intervening cycles

between transactions. Therefore, the throughput is 11.1 Mbytes per second.

Mode 4 Interfacing Topology

demonstrates one of the topologies used to connect Slowport to the Intel and AMCC*

SONET/SDH device.

Similar to the Lucent* TDAT042G5 interface, the address and the data need demultiplexing. It

requires a total of six buffers.

The RD_L, WR_L, and CS_L[1] entirely match the E, RWB, and CSB pins respectively, in the

Intel framer configured to Motorola* mode. However, the INT has to be connected to the

SP_ACK_L as the PMC-Sierra* Interface does. The ALE pin can share the SP_CP. However, if it

does not meet the timing, the ALE pin can be tied high as shown in

.

Figure 51. Mode 3 Single Read Transfer Followed by Write (B0)

B1752-07

SP_CLK

SP_ALE_L

SP_CS_L[1] /CSB

SP_WR_L/WRB

SP_RD_L/RDB

2

0

4

6

8

10

12

14

16

18

20

22

24

SP_AD[7:0]

SP_ACK_L /INT

SP_CP

SP_OE_L

A[10:1]

SP_DIR

ADDR[15:0]

DATA[15:0]

A

[15:8]

A

[7:0]

A

[15:8]

D

[7:0]

A

[7:0]

A

[7:0]

D[7:0]

D[15:8]

A[15:8]

D[15:0]

D[15:0]

D[15:0]

D[15:0]

2xD[15:8]

A

[7:0]

A

[10:8]

A

[10:8]

D[15:8]

A[10:1]

A

[7:0]