3 address spaces for xpi internal devices – Intel NETWORK PROCESSOR IXP2800 User Manual

Page 136

136

Hardware Reference Manual

Intel

®

IXP2800 Network Processor

Intel XScale

®

Core

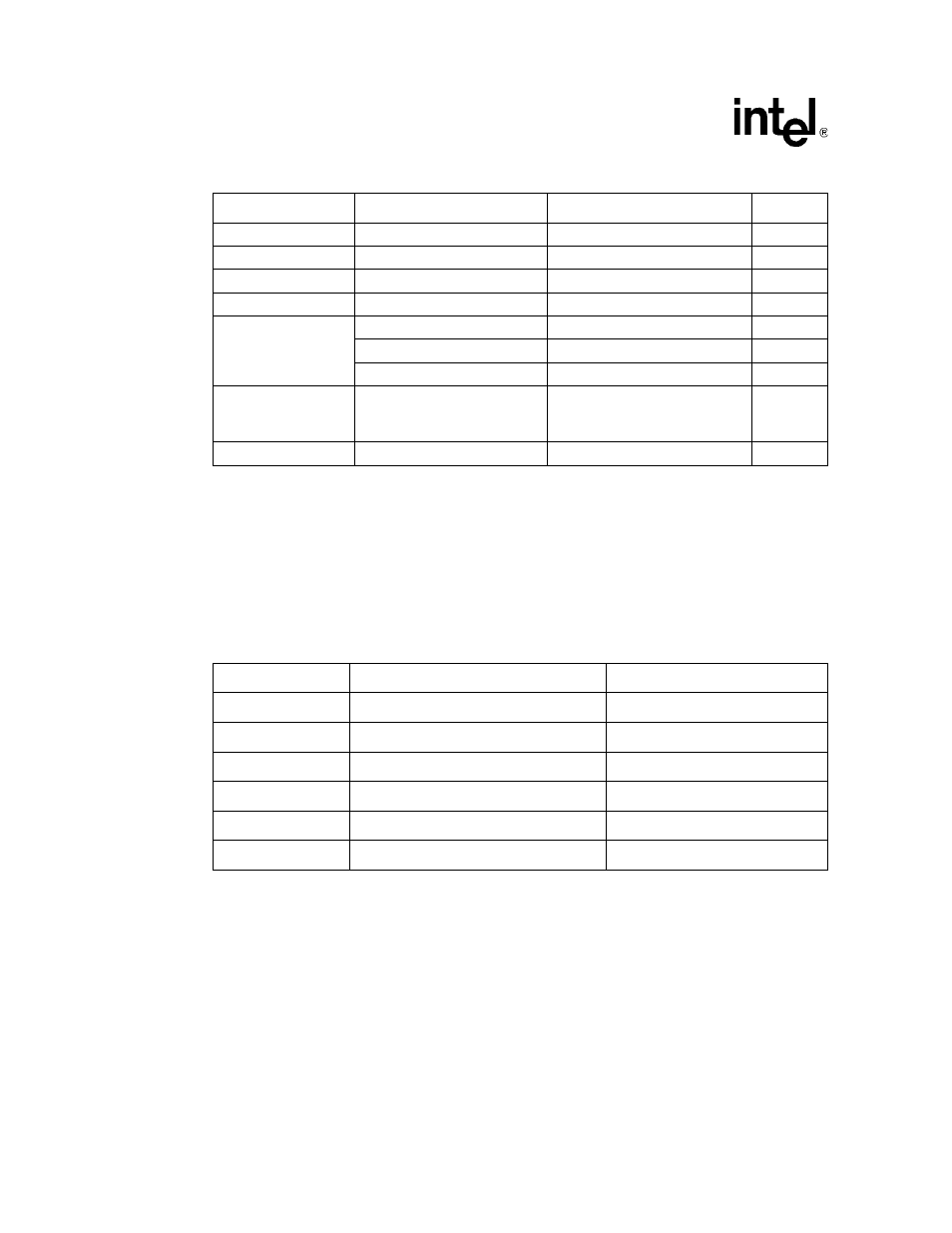

3.12.1.3

Address Spaces for XPI Internal Devices

shows the address space assignment for XPI devices.

Table 52. Data Transaction Alignment

Interface Units

APB Bus

Read

Write

GRegs

32 bits

32 bits

32 bits

UART

32 bits

32 bits

32 bits

GPIO

32 bits

32 bits

32 bits

Timer

32 bits

32 bits

32 bits

Slowport

Microprocessor Access

8 bits

8 bits

8 bits

16 bits

16 bits

16 bits

32 bits

32 bits

32 bits

Slowport

Flash Memory Access

1

1.

The flash memory interface only supports 8-bit wide flash devices. APB write transactions are assumed to be 8-bits wide,

and correspond to one write cycle at the flash interface. APB read transactions are assumed to be 32-bits wide, and corre-

spond to four flash read cycles for the 32-bit read mode set in the SP_FRM register. However, for the flash register read

mode (8-bit read mode), it only needs one flash read cycle of 8-bit data and passes it back to APB directly. By default, the

32-bit read mode is set. It is advisable to stay in this mode most of the time and not change them dynamically during ac-

cesses.

32 bits for 32-bit read mode, 8

bits for register read mode;

8 bits for write;

Assemble 8 bits into 32-bit data for

32-bit read mode; 8 bits for register

read mode (8-bit read mode).

8 bits

CSR Access

32 bits

32 bits

32 bits

Table 53. Address Spaces for XPI Internal Devices

Units

Starting Address

Ending Address

GPIO

0xC0010000

0xC0010040

TIMER

0xC0020000

0xC0020040

UART

0xC0030000

0xC003001C

PMU

0xC0050000

0xC0050E00

Slowport CSR

0xC0080000

0xC0080028

Slowport Device

0xC4000000

0xC7FFFFFF