Maxim Integrated DS33Z41 User Manual

Page 98

DS33Z41 Quad IMUX Ethernet Mapper

98 of 167

Register Name:

LI.TRX86SAPIL

Register Description:

Transmit Receive X.86 SAPIL

Register Address:

0DCh

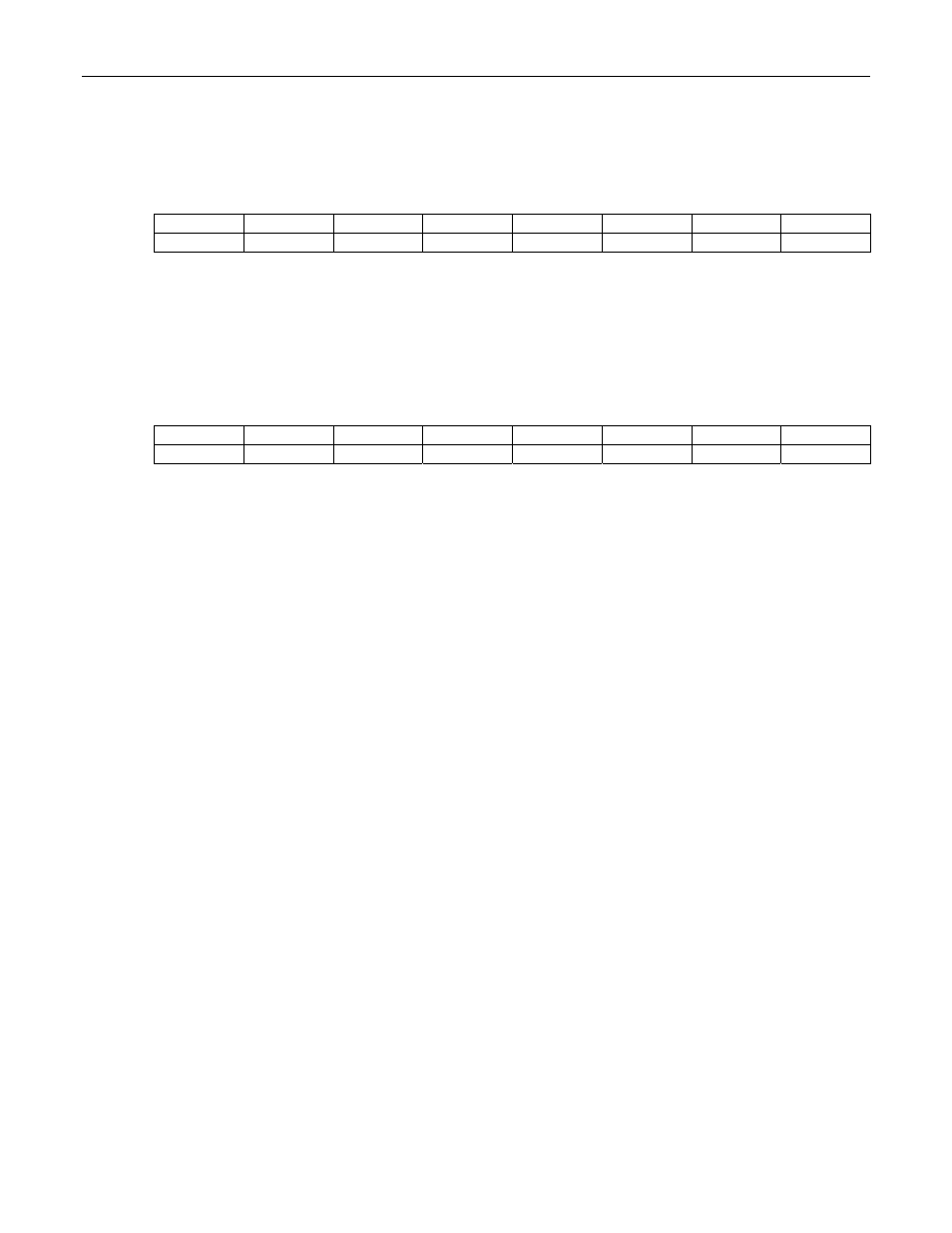

Bit

# 7 6 5 4 3 2 1 0

Name

TRSAPIL7 TRSAPIL6 TRSAPIL5 TRSAPIL4 TRSAPIL3 TRSAPIL2 TRSAPIL1 TRSAPIL0

Default

0 0 0 0 0 0 0 1

Bits 7 to 0: X86 Transmit Receive Control (TRSAPIL7 to TRSAPIL0). This is the address field for the X.86

transmitter and expected value for the receiver. The register is reset to 0x01.

Register Name:

LI.CIR

Register Description:

Committed Information Rate

Register Address:

0DDh

Bit

# 7 6 5 4 3 2 1 0

Name CIRE CIR6 CIR5 CIR4 CIR3 CIR2 CIR1 CIR0

Default

0 0 0 0 0 0 0 1

Bit 7: Committed Information Rate Enable (CIRE). Set this bit to 1 to enable the Committed Information Rate

Controller feature.

Bits 6 to 0: Committed Information Rate (CIR6 to CIR0). These bits provide the value for the committed

information rate. The value is multiplied by 500kbps to get the CIR value. The user must ensure that the CIR

value is less than or equal to the maximum Serial Interface transmit rate. The valid range is from 1 to 104. Any

values outside this range will result in unpredictable behavior. Note that a value of 104 translates to a 52Mbps line

rate. Hence if the CIR is above the line rate, the rate is not restricted by the CIR. For instance, if using a T1 line

and the CIR is programmed with a value of 104, it has no effect in restricting the rate.