Maxim Integrated DS33Z41 User Manual

Page 76

DS33Z41 Quad IMUX Ethernet Mapper

76 of 167

Register Name:

GL.IMXSLS

Register Description:

Inverse MUX Sync Latched Status

Register Address:

1Ah

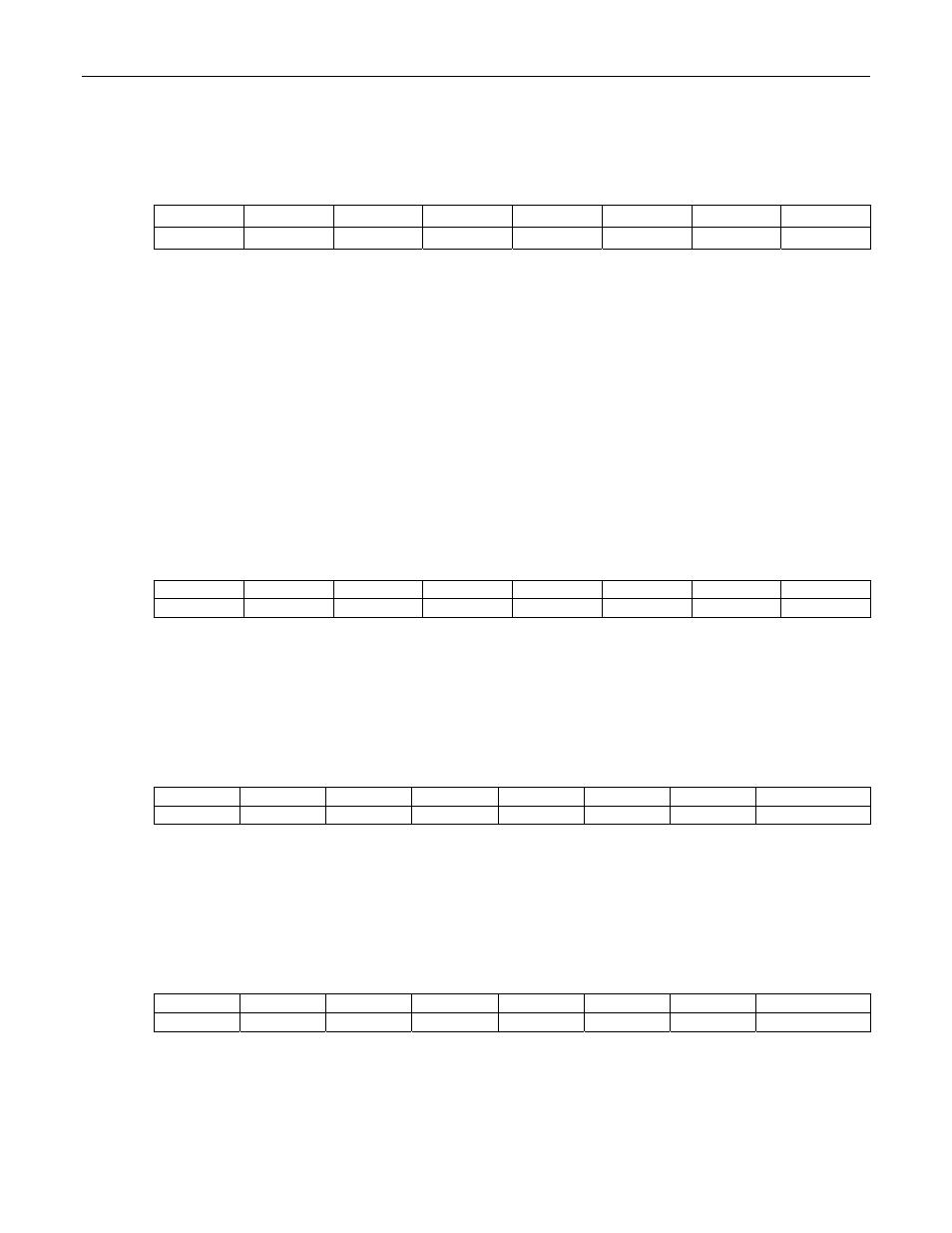

Bit #

7 6 5 4 3 2 1 0

Name

ITSYNCLS4 ITSYNCLS3 ITSYNCLS2 ITSYNCLS1 IRSYNCLS4 IRSYNCLS3 IRSYNCLS2 IRSYNCLS1

Default

0 0 0 0 0 0 0 0

Bit 7: IMUX Transmit Sync Latched Status 4 (ITSYNCLS4). This is a latched status bit for ITSYNC4.

Bit 6: IMUX Transmit Sync Latched Status 3 (ITSYNCLS3). This is a latched status bit for ITSYNC3.

Bit 5: IMUX Transmit Sync Latched Status 2 (ITSYNCLS2). This is a latched status bit for ITSYNC2.

Bit 4: IMUX Transmit Sync Latched Status 1 (ITSYNCLS1). This is a latched status bit for ITSYNC1.

Bit 3: IMUX Receive Sync Latched Status 4 (IRSYNCLS4). This is a latched status bit for IRSYNC4.

Bit 2: IMUX Receive Sync Latched Status 3 (IRSYNCLS3). This is a latched status bit for IRSYNC3.

Bit 1: IMUX Receive Sync Latched Status 2 (IRSYNCLS2). This is a latched status bit for IRSYNC2.

Bit 0: IMUX Receive Sync Latched Status 1 (IRSYNCLS1). This is a latched status bit for IRSYNC1.

Register Name:

GL.IMXDFD

Register Description:

Inverse MUX Diff Delay

Register Address:

1Bh

Bit

# 7 6 5 4 3 2 1 0

Name IMUXDFD7 IMUXDFD6 IMUXDFD5 IMUXDFD4 IMUXDFD3 IMUXDFD2 IMUXDFD1 IMUXDFD0

Default

0 0 0 0 0 0 0 0

Bits 7 to 0 IMUX Differential Delay. These 8 bits provide the IMUX differential delay. The maximum differential

delay that can be measured is 64ms.

Register Name:

GL.IMXDFEIE

Register Description:

Inverse MUX Diff Delay Error Interrupt Enable

Register Address:

1Ch

Bit

# 7 6 5 4 3 2 1 0

Name — — —

— —

— —

IDDEIE

Default

0 0 0 0 0 0 0 0

Bit 0: IMUX Differential Delay Error Interrupt Enable (IDDEIE). Setting this bit to 1 enables an interrupt on

IDDELS0.

Register Name:

GL.IMXDFDELS

Register Description:

Inverse MUX Diff Delay Error Latched Status

Register Address:

1Dh

Bit

# 7 6 5 4 3 2 1 0

Name — — — — — — —

IDDELS0

Default

0 0 0 0 0 0 0 0

Bit 0: IMUX Differential Delay Error latched Status (IDDELS0). This bit provides the differential delay error

latched status. It is set to 1 when the differential delay has exceeded 7.75ms.